# MITSUBISHI SOUND PROCESSOR ICS M51581FP/GP DIGITAL AUDIO INTERFACE (DAI)

### DESCRIPTION

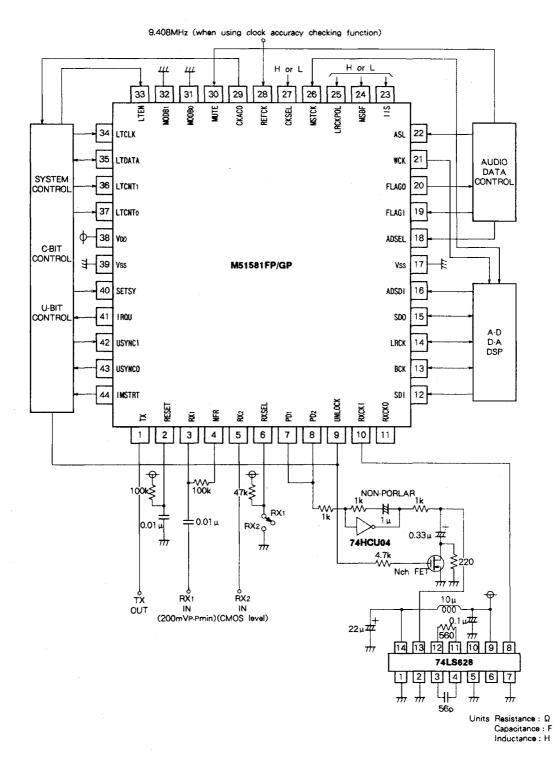

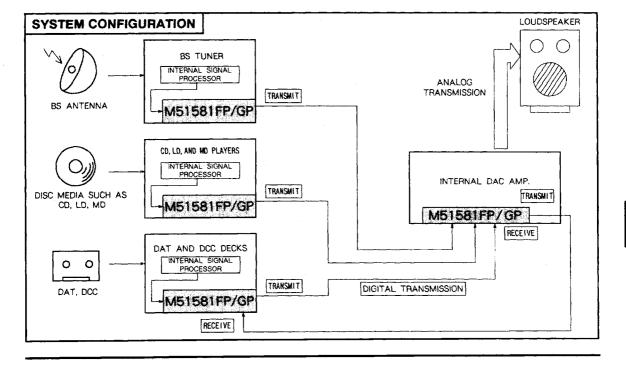

The M51581 is a semiconductor IC for transmitting and receiving signals formed according to a digital audio interface format conforming to the EIAJ standards. It has a variety of functions as it supports both professional and consumer modes and can be applied to the serial copy management systems (SCMS). The IC enables the engineer to configure an optimum digital audio interface for DAT, DCC, MD, and CD-R systems.

### FEATURES

- Capable of dealing with audio data up to 24-bit

- Adaptable to both the I<sup>2</sup>S and non-I<sup>2</sup>S audio interface formats

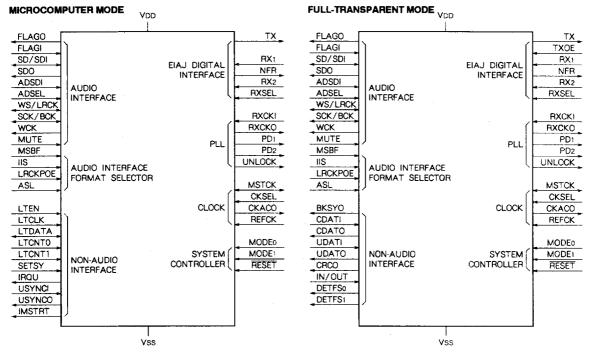

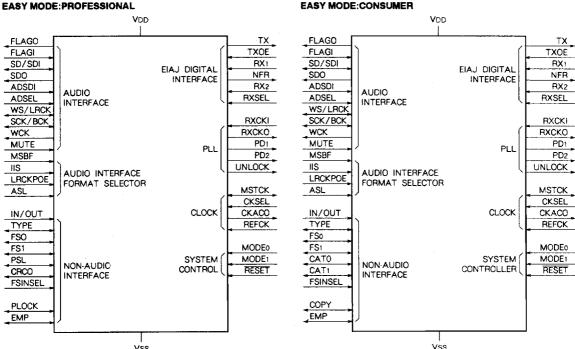

- Selection available from three kinds of control methods (microcomputer, easy, and full-transparent modes)

- Two channels of signal input pins for reception

- Feedthrough function equipped

- Level converter for converting the level of received signals into CMOS level (minimum input level : 200mVp-p)

- Supports both consumer and professional modes

### **RECOMMENDED OPERATING CONDITIONS**

| Supply voltage range | Voo ≈ 4.5 to 5.5V |

|----------------------|-------------------|

| Rated supply voltage |                   |

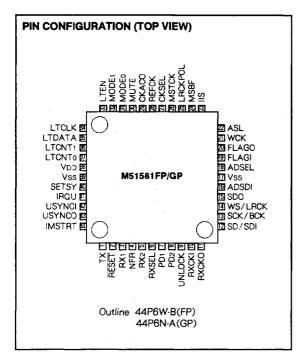

Outline 44P6W-B(FP) 1.0mm pitch QFP (13.2mm × 13.2mm × 2.0mm)

Outline 44P6N-A(GP) 0.8mm pitch QFP (10.0mm × 10.0mm × 2.8mm)

**MITSUBISHI SOUND PROCESSOR ICs**

## M51581FP/GP

**DIGITAL AUDIO INTERFACE (DAI)**

## **DIGITAL AUDIO INTERFACE (DAI)**

### **PIN DESCRIPTION**

COMMON PINS (O" and Bi denote tri-state output and bi-directional transmission, respectively.)

| Pin No. | Name    | 1/0       | Function                                                                                                                                                         |  |  |  |  |

|---------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0       | ТХ      | 0"        | Digital audio data output in EIAJ format                                                                                                                         |  |  |  |  |

| 2       | RESET   | 1         | Reset : "0" = reset (in microcomputer mode : fs = 48kHz, TX disabled)                                                                                            |  |  |  |  |

| 3       | RX1     | I         | Digital audio data input 1 in EIAJ format : for input via coaxial cable(200mVp-p min.)                                                                           |  |  |  |  |

| 4       | NFR     | 0         | RX1 level converter output (Connect a feedback resistor.)                                                                                                        |  |  |  |  |

| 5       | RX2     |           | Digital audio data input 2 in EIAJ format : for input via optical cable(CMCS level)                                                                              |  |  |  |  |

| 6       | RXSEL   | l         | RX input selection : " $1$ " = RX <sub>1</sub> ; " $0$ " = RX <sub>2</sub> .<br>In microcomputer mode, this pin is for selecting the polarity of RXSEL           |  |  |  |  |

| Ø       | PD1     | 0         | Output of phase detector for charge pump VCO                                                                                                                     |  |  |  |  |

| 8       | PD2     | 0         |                                                                                                                                                                  |  |  |  |  |

| 9       | UNLOCK  | 0         | Output of unlock detector: "1" = unlock                                                                                                                          |  |  |  |  |

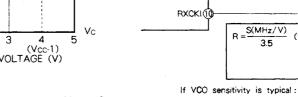

| 0       | RXCKI   | · · · · · | VCO clock input (256fs)                                                                                                                                          |  |  |  |  |

| 0       | RXCKO   | 0         | VCO clock output (RXCKI)                                                                                                                                         |  |  |  |  |

| 12      | SD/SDI  | Bi/I      | Serial audio data input/output (input only except for I2S format)                                                                                                |  |  |  |  |

| 13      | SCK/BCK | Bi        | Audio data bit clock input/output                                                                                                                                |  |  |  |  |

| 14      | WS/LRCK | Bi        | Audio data word select input/output                                                                                                                              |  |  |  |  |

| 15      | SDO     | 0         | Serial audio data output                                                                                                                                         |  |  |  |  |

| 16      | ADSDI   | 1         | Serial audio data input from AD converter                                                                                                                        |  |  |  |  |

| Ŵ       | Vss     | -         | Ground                                                                                                                                                           |  |  |  |  |

| 18      | ADSEL   | . 1       | Serial audio data source selection : "1" = analog (AD converter) ; "0" = digital (RX) ; in microcomputer mode, this pin is for selecting the polarity of $ADSEL$ |  |  |  |  |

| (19)    | FLAGI   |           | Error flag input                                                                                                                                                 |  |  |  |  |

| 0       | FLAGO   | 0         | Error flag output                                                                                                                                                |  |  |  |  |

| Ø       | WCK     | 0"        | Word clock output (2fs at reception)                                                                                                                             |  |  |  |  |

| 0       | ASL     | 1         | Audio data sampling length selection : "1" = 24 bits ; "0" = 16 bits                                                                                             |  |  |  |  |

| 3       | IIS     | 1         | Audio data format selection : " $1$ " = $1^2$ S ; " $0$ " = Any other format than $1^2$ S                                                                        |  |  |  |  |

| 29      | MSBF    |           | MSB selection : "1" = MSB first ; "0" = LSB first                                                                                                                |  |  |  |  |

| Ø       | LRCKPOL | 1         | LRCK polarity selection : "1" = Lch $\rightarrow$ 1 ; "0" = Lch $\rightarrow$ 0                                                                                  |  |  |  |  |

| 8       | MSTCK   | Bi        | Master clock input/output (128fs or 256fs)                                                                                                                       |  |  |  |  |

| Ø       | CKSEL   | I         | Master clock frequency selection : "0" = 256fs ; "1" = 128fs                                                                                                     |  |  |  |  |

| 8       | REFCK   | I         | Reference clock input for checking the accuracy of sampling frequency (9.408MHz)                                                                                 |  |  |  |  |

| 8       | CKACO   | 0         | Checking result output of the accuracy of sampling frequency:<br>"1" = $\pm 0.14\%$ or more of frequency error                                                   |  |  |  |  |

| 30      | MUTE    | ł         | Mute control : "1" = mute ; In microcomputer mode, this pin is for selecting the polarity of mute control                                                        |  |  |  |  |

| 3)      | MODEo   | I         | Mode selection : (MODE1, MODE0) "0, 0" = microcomputer mode<br>"0, 1" = easy mode                                                                                |  |  |  |  |

| 100     | MODE1   | 1         | "1, 0" = full-transparent mode<br>"1, 1" = test mode                                                                                                             |  |  |  |  |

| 38      | VDD     | -         | Power supply                                                                                                                                                     |  |  |  |  |

| 39      | Vss     |           | Ground                                                                                                                                                           |  |  |  |  |

### **DIGITAL AUDIO INTERFACE (DAI)**

| Pin No. | Name    | 1/0 | Function                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 33      | IN/OUT  | 1   | Transmission selection : "1" = receive ; "0" = transmit                                                                                                                                                                                                                                                     |  |  |  |  |

| 39      | PSL     | Bi  | Professional audio data sampling length selection:"1"=24 bits; "0"=20 bits                                                                                                                                                                                                                                  |  |  |  |  |

| 39      | CRCO    | 0   | CRC checking result output : "1" = error                                                                                                                                                                                                                                                                    |  |  |  |  |

| 39      | TXOE    |     | TX output enable : "1" = enable                                                                                                                                                                                                                                                                             |  |  |  |  |

| Ø       | FSINSEL | 1   | fs information selection(in reception) : "0" = fs information on C-bits, "1" = detected fs                                                                                                                                                                                                                  |  |  |  |  |

| ۵)      | TYPE    | Bi  | Type information "1" = Type I (professional = "1")                                                                                                                                                                                                                                                          |  |  |  |  |

| 4       | FS0     | Bi  | fs information (in transmission : input) fs information (in reception : output)                                                                                                                                                                                                                             |  |  |  |  |

|         |         |     | fs information on Detected fs<br>C-bits(FSINSEL = "0"); (FSINSEL = "1")                                                                                                                                                                                                                                     |  |  |  |  |

| æ       | FS1     | Ві  | (FSo, FS1) "0, 0" = 48kHz default<br>"0, 1" = 48kHz       "0, 0" = 48kHz default<br>"0, 1" = 48kHz       "0, 0" = 48kHz default<br>"0, 1" = 48kHz       44.1kHz = "0, 0"<br>48kHz = "1, 0"         "1, 0" = 44.1kHz       "1, 0" = 44.1kHz       32kHz = "1, 1"         "1, 1" = 32kHz       "1, 1" = 32kHz |  |  |  |  |

| 43      | PLOCK   | Bi  | Source lock information : "1" = unlock                                                                                                                                                                                                                                                                      |  |  |  |  |

| 44      | EMP     | Bi  | Emphasis information : "1" = $50\mu/15\mu$ sec                                                                                                                                                                                                                                                              |  |  |  |  |

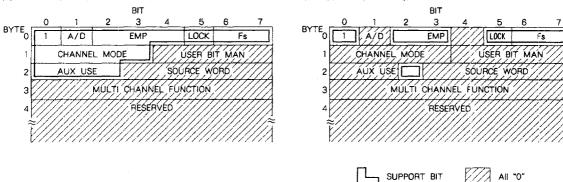

### EASY MODE (PROFFESIONAL), (at @pin "TYPE"="1")

### EASY MODE (CONSUMER), (at @pin "TYPE"="0")

| Pin No.  | Name    | 1/0 | Function                                                                                                                                 |  |  |  |  |

|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3        | IN/OUT  | 1   | Transmission selection : "1" = receive ; "0" = transmit                                                                                  |  |  |  |  |

| 39       | CATO    | Bi  | Category information : (CAT1, CAT0) "0, 0" = general<br>"0, 1" = CD                                                                      |  |  |  |  |

| \$9      | CAT1    | Bi  | "1, 0" = BS<br>"1, 1" = DAT                                                                                                              |  |  |  |  |

| 39       | TXOE    | 1   | TX output enable : "1" = enable ; "0" = disable (high impedance)                                                                         |  |  |  |  |

| 8        | FSINSEL | 1   | fs information selection(in reception) : "0" = fs information on C-bits ; "1" = detected fs                                              |  |  |  |  |

| <b>@</b> | TYPE    | Bi  | Type information : "0" = Type II (consumer = "0")                                                                                        |  |  |  |  |

| ٩        | FSo     | Bi  | fs information (in transmission : input)<br>fs information (in reception)<br>fs information on<br>C-bits(FSINSEL = "0"); (FSINSEL = "1") |  |  |  |  |

| Ø        | FS1     | Bi  |                                                                                                                                          |  |  |  |  |

| ٩        | COPY    | Bi  | Copy information : "1" = enable                                                                                                          |  |  |  |  |

| 49       | EMP     | Bi  | Emphasis information : "1" = $50 \mu / 15 \mu sec$                                                                                       |  |  |  |  |

### **DIGITAL AUDIO INTERFACE (DAI)**

### MICROCOMPUTER MODE (LT BUS MODE)

| Pin No.     | Name   | 1/0 | Function                                        |                     |

|-------------|--------|-----|-------------------------------------------------|---------------------|

| 39          | LTEN   |     | LT interface enable : "1" = enable              |                     |

| 39          | LTCLK  | 1   | Bit clock input for LT interface data           |                     |

| \$          | LTDATA | Bi  | LT interface data input/output                  |                     |

| 39          | LTCNT1 | 1   | LT interface control : (LTCNT1, LTCNT0)         | "0, 0" = C·bit data |

|             |        |     |                                                 | "0, 1" = U-bit data |

| 3           | LTCNTo |     |                                                 | "1, 0" = setting    |

|             |        |     |                                                 | "1, 1" = status     |

| 40          | SETSY  | 1   | Setting latch clock input                       |                     |

| <b>(1</b> ) | IRQU   | 0   | U-bit data information message indicator out    | put                 |

| Ø           | USYNCI | 1   | U-bit data unit indicator input (in transmissio | on)                 |

| 4           | USYNCO | 0"  | U-bit data unit indicator output (in reception  | )                   |

| •           | IMSTRT | 0   | U-bit data message start indicator output       |                     |

### FULL-TRANSPARENT MODE

| Pin No. | Name   | 1/0 | Function                                                |

|---------|--------|-----|---------------------------------------------------------|

| 3       | IN/OUT |     | Transmission selection : "1" = receive ; "0" = transmit |

| 39      | BKSYO  | 0   | C-bit block sink output (preamble "B" detected)         |

| \$      | CRCO   | 0   | CRC check output : "1" = error                          |

| 39      | TXOE   | 1   | TX output enable : "1" = enable                         |

| ٧       | DETFS0 | 0   | Detected fs                                             |

|         |        |     | $(DETFS_0, DETFS_1)$ 44.1kHz = "0, 0"                   |

| ٩       | DETFS1 | 0   | 48kHz = "1, 0"                                          |

|         |        |     | 32kHz = "1, 1"                                          |

| 4       | CDAT1  | 1   | C-bit data input                                        |

| Ø       | CDATO  | 0   | C-bit data output                                       |

| 43      | UDATI  |     | U-bit data input                                        |

| •       | UDATO  | 0   | U-bit data input                                        |

### **DIGITAL AUDIO INTERFACE (DAI)**

#### ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C, unless otherwise noted)

| Symbol | Parameter             |      | Ratings |          |        |  |

|--------|-----------------------|------|---------|----------|--------|--|

|        | Farameter             | Min  | Тур     | Max      | Unit   |  |

| VDD    | Supply voltage        | -0.3 |         | 6.5      | V      |  |

| Pd     | Power dissipation     | -    | -       | 600      | m₩     |  |

| Vi     | Input voltage         | -0.3 | -       | Voo+0. 3 | V      |  |

| Vo     | Output voltage        | -0.3 | -       | Vod+0. 3 | V      |  |

| lo     | Output current        |      | -       | ± 16     | mA     |  |

| Topr   | Operating temperature | -30  | -       | 70       | ទ      |  |

| Tstg   | Storage temperature   | -50  | _       | 125      | ູ<br>ໃ |  |

#### RECOMMENDED OPERATING CONDITIONS (VDD = 5V, Ta = - 30 °C to 70 °C)

| C. mb . I | Promotor                   | Test conditions                |      | Limits |      |      |  |

|-----------|----------------------------|--------------------------------|------|--------|------|------|--|

| Symbol    | Parameter                  | l'est conditions               | Min  | Тур    | Max  | Unit |  |

| VDD       | Supply voltage             |                                | 4.5  | 5.0    | 5.5  | V    |  |

| VIL       | Input voltage ("L" level)  | $V_{DD} = 4.5V$                | . 0  | -      | 1.35 | V    |  |

| ViH       | Input voltage ("H" level)  | V <sub>DD</sub> = 5.5          | 3.85 | -      | VDD  | V    |  |

| tri       | Input rise time            |                                | -    | I      | 500  | ns   |  |

| tfi       | Input fall time            |                                | - 1  | -      | 500  | ns   |  |

| Li        | Input leak current         | $V_{I} = 0$ , $V_{DD}$         | -    | -      | ± 1  | μA   |  |

| IOL       | Output current ("L" level) | $V_{OL} = 0.4V, V_{DD} = 4.5V$ | 14   |        |      | mA   |  |

| Іон       | Output current ("H" level) | $V_{OH} = 4.1V, V_{DD} = 4.5V$ | -    | -      | - 5  | mA   |  |

| Vol       | Output voltage ("L" level) | lo_ < 1 μA                     | 4.95 | -      | -    | V    |  |

| Voн       | Output voltage ("H" level) | Ιοн < - 1 μΑ                   | -    | ·      | 0.05 | V    |  |

All inputs are at CMOS level

#### **FUNCTION DESCRIPTION**

#### 1. Reset conditions

#### (1) Reset action

- (a) All setting bits are set to 0 (in microcomputer mode) Transmission mode ADSEL, TEST, BCKPOL, MUTE, RXSEL, TXOE, NOWD = 0

- (b) The lock detector is initialized

- (c) The sampling frequency accuracy checker is initialized

#### (2) Master clock

White resetting, the master clock should not necessarily be supplied. (It is also permissible to supply it.)

#### (3) Reset time

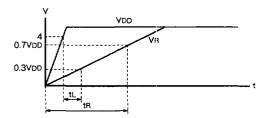

#### **RECOMMENDED OPERATING CONDITIONS FOR RESETTING**

| Remetter |                    | Test conditions                    | Limits |     |     | 11-14 |

|----------|--------------------|------------------------------------|--------|-----|-----|-------|

| Symbol   | Parameter          |                                    | Min    | Тур | Max | Unit  |

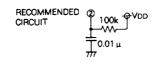

| tL       | L level hold time  | $V_{DD} > 4V$ to $V_R < 0.3V_{DD}$ | 50     | -   | -   | μs    |

| tR       | L level reset time | $V_{DD} = 5V, CR = 100k/0.01 \mu$  |        | 1.2 | ļ   | ms    |

## 2. RECOMMENDED OPERATING CONDITIONS FOR RX1 INPUT VOLTAGE

|        |                   | Test conditions | Limits |     |     |      |

|--------|-------------------|-----------------|--------|-----|-----|------|

| Symbol | Symbol Parameter  | Test conditions | Min    | Тур | Max | Unit |

| VIBX1  | RX1 input voltage | fs < 50kHz      | 200m   | -   | VDD | Vp.p |

### **DIGITAL AUDIO INTERFACE (DAI)**

#### 3. Audio Interface

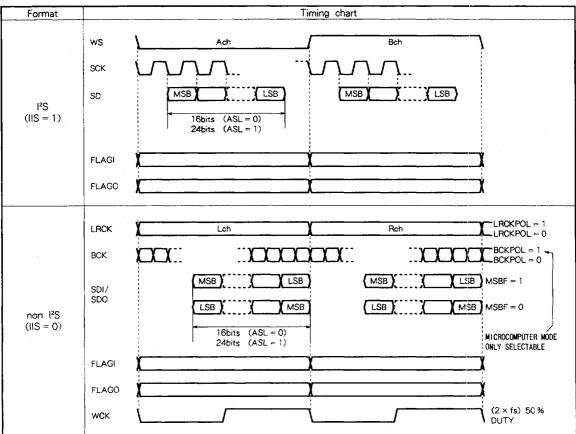

(1) Format

(2) Number of significant bits 16bits/24bits

I2S/non-I2S

(3) Error flag

If one of the following conditions occurs in reception mode, an error flag is sent

- Validity flag = 1(error)

- Parity check result = 1(error)

- PLL does not lock

#### (4) Preceding-value holding

If the result of parity check is an error, the preceding value in audio data is held

#### (5) Mute

If PLL is unlocked in reception mode, the signal is muted automatically. In addition, it is possible to mute a signal compulsively with the MUTE pin

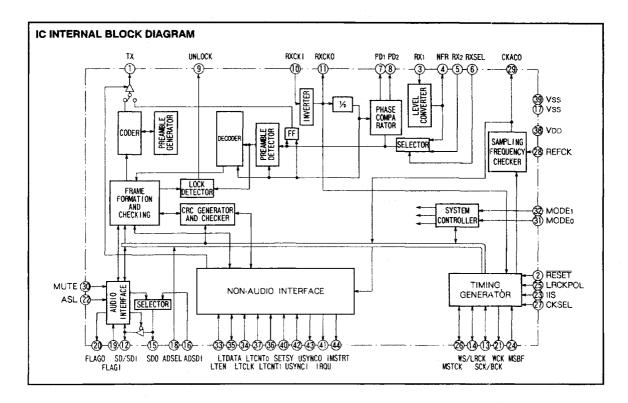

#### 4. Non audio interface

Non audio data includes the following

- Channel status

- User data

- Settings (to set IC operating conditions)

- Status (Monitored IC operating conditions)

Control methods as shown below are available for non audio data

MODE00 - Microcomputer mode

In this mode the M51581FP is controlled by a microcomputer via LT bus by serial data

MODE01 - Easy mode

The M51581FP is controlled by means of dedicated pins MODE10 - Full-transparent mode

In this mode a microcomputer is used to receive and process all bits of both C and U bits

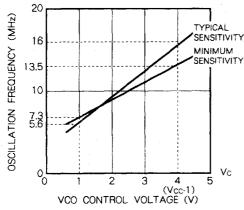

#### 5. Checking the accuracy of sampling frequency

It is possible by means of the sampling frequency checker to check whether received signals are within approximately  $\pm 0.14\%$  of the reference value. With this checking function, recorded patterns on a DAT tape and the like are prevented from shifting. It is also possible to judge to which range of the three reference values (32k, 44.1k, or 48kHz) the sampling frequency of the received signal correspond (fs detection function). If these functions, sampling frequency accuracy check and fs detection, are not used, pin **@** REFCK does not require the reference clock.

Fix pin 29 to L in that case.

#### 6. PLL lock detection

In the following conditions, PLL is judged to be unlocked

- No preamble has been detected

- Parity check resulted in two consecutive errors

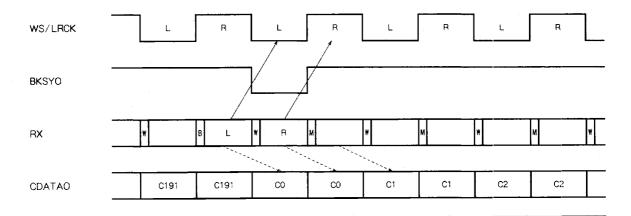

#### TIMING CHART

#### **1. AUDIO INTERFACE FORMAT**

(1) Audio Interface format conditions

|     | Selection pin |         | Format  | Audio data                                        | WS/LRCK            |

|-----|---------------|---------|---------|---------------------------------------------------|--------------------|

| 115 | MSBF          | LRCKPOL | TOLMAL  |                                                   |                    |

| 1   | 1             | 0       | I²S     | MSB first<br>16bits (ASL = 0)<br>24bits (ASL = 1) |                    |

|     | 1             | 0       |         | 1                                                 | Lch = 0<br>Rch = 1 |

|     | 1             | 1       | non-l²S | <br>↑                                             | Lch = 1<br>Rch = 0 |

| 0   | 0             | 0       |         | LSB first<br>16bits (ASL = 0)<br>24bits (ASL = 1) | Lch = 0<br>Rch = 1 |

|     | 0             | 1       |         | t                                                 | Lch = 1<br>Rch = 0 |

### **DIGITAL AUDIO INTERFACE (DAI)**

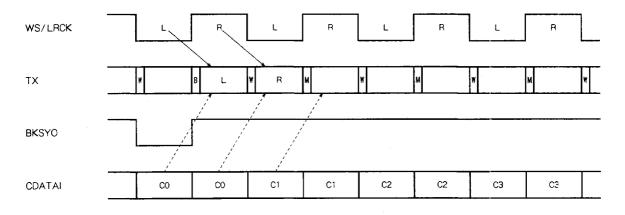

#### (2) Audio interface format timing chart

## **DIGITAL AUDIO INTERFACE (DAI)**

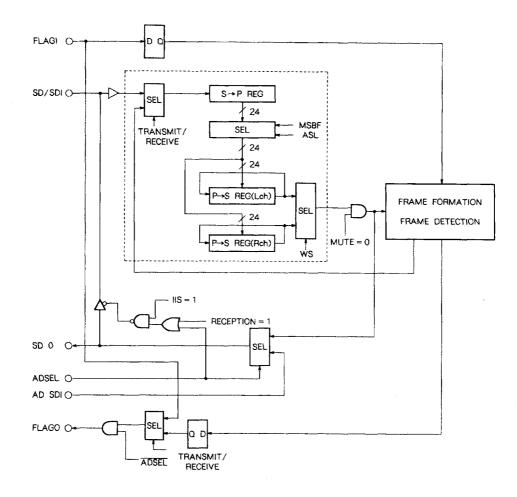

#### (3) Audio interface block diagram

#### (4) Operation status of FLAGO, SD/SDI

|                       |                     |       | l <sup>2</sup> S           |                              | non-l <sup>2</sup> S       |        |

|-----------------------|---------------------|-------|----------------------------|------------------------------|----------------------------|--------|

| DAT operation<br>mode | DAI<br>transmission | ADSEL | FLAGO                      | SD/SDI                       | FLAGO                      | SD/SDI |

| Reproduction          | Transmit            | "0"   | FLAGI                      | Input                        | FLAGI                      | Input  |

| Analog recording      | Transmit            | "1"   | "0"                        | Output<br>(ADSDI)            | "0"                        | Input  |

| Digital recording     | Receive             | "0"   | Data on received<br>V bits | Output<br>(received<br>data) | Data on received<br>V bits | Input  |

## **DIGITAL AUDIO INTERFACE (DAI)**

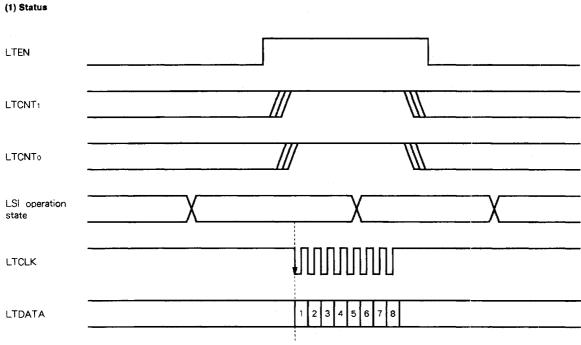

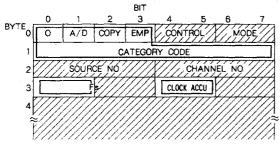

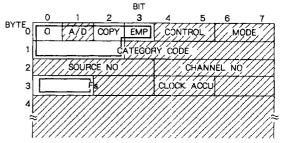

### 2. MICROCOMPUTER MODE DATA FORMAT

### (1) LTDATA selection

|      | Signal name |                    | Data contents of LTDATA     |

|------|-------------|--------------------|-----------------------------|

| LTEN | LTCNT1      | LTCNT <sub>0</sub> | Data contents of LIDATA     |

| 1    | 0           | 0                  | C-bit data                  |

| 1    | 0           | 1                  | U-bit data                  |

| 1    | 1           | 0                  | Setting (microcomputer→DAI) |

| 1    | 1           | 1                  | Status (DAI→microcomputer)  |

| (2) Setting | 2) Settings (8-bit) 1 2 3 4 5 6 7 8                                                               |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit         | Function                                                                                          |  |  |  |  |  |

| 1           | Transmission selection : "1" = receive, "0" = transmit                                            |  |  |  |  |  |

| 2           | ADSEL : Serial audio data source selection ;<br>Polarity is determined by ADSEL (pin 18).(Note 1) |  |  |  |  |  |

| 3           | Test : Fixed to "0" normally                                                                      |  |  |  |  |  |

| 4           | BCKPOL:Bit clock(BCK)polarity selection; (f this bit is "0," BCK falls at LRCK edges              |  |  |  |  |  |

| 5           | MUTE : Mute control ; Polarity is determined by MUTE(pin 30).(Note 1)                             |  |  |  |  |  |

| 6           | RXSEL:RX input selection;Polarity is determined by RXSEL(pin 6)(Note 1)                           |  |  |  |  |  |

| 7           | TXOE : TX output enable ; "1" = enable                                                            |  |  |  |  |  |

| 8           | NOWD : Timing control for USYNCI and USYNCO ; "0" = no delay<br>"1" = 4WS delay                   |  |  |  |  |  |

| (3) Status | (8-bit) (8-bit) 1 2 3 4 5 6 7 8                                                                    |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit        | Function                                                                                           |  |  |  |  |  |  |

| 1          | UNLOCK : PLL unlock information ; "1" = unlock                                                     |  |  |  |  |  |  |

| 2          | CKACO : Output sampling frequency accuracy check ; "1" = frequency error greater than $\pm 0.14\%$ |  |  |  |  |  |  |

| 3          | DETFS0 Detected fs                                                                                 |  |  |  |  |  |  |

|            | (DETFS0, DETFS1) 44.1kHz ≈ "0, 0"                                                                  |  |  |  |  |  |  |

| 4          | DETFS1 48kHz = "1, 0"                                                                              |  |  |  |  |  |  |

|            | 32kHz = "1, 1"                                                                                     |  |  |  |  |  |  |

(Note 1) In microcomputer mode, functions listed below are determined by the polarity of both the dedicated pins and setting bits.

| Name  | Function                           | Polarity<br>dedicated |            |       | Polarity of setting bits                                   |

|-------|------------------------------------|-----------------------|------------|-------|------------------------------------------------------------|

| ADSEL | Serial audio data source selection | ADSEL<br>(18) pin     | "0"<br>"1" | Bit 2 | "1" = analog, "0" = digital<br>"0" = analog, "1" = digital |

| MUTE  | Mute control                       | MUTE<br>30 pin        | "0"<br>"1" | Bit 5 | "1" = mute                                                 |

| RXSEL | RX input selection                 | RXSEL                 | "0"<br>"1" | Bit 6 | "1"= RX1, "0"= RX2<br>"0"= RX1, "1"= RX2                   |

## **DIGITAL AUDIO INTERFACE (DAI)**

### PIN DESCRIPTION (Microcomputer mode, pins for LT bus)

| Pin No.        | Name             | 1/0 | Function and timing                                                                                                                                                                                                                                                                                                                         |

|----------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39             | LTEN             | 1   | Enable control signal for LTDATA                                                                                                                                                                                                                                                                                                            |

|                |                  |     | LTEN ENABLE                                                                                                                                                                                                                                                                                                                                 |

|                |                  |     | LTDATA DISABLE DISABLE (Hi-z)                                                                                                                                                                                                                                                                                                               |

|                |                  |     | When LTEN = 0, the input to LTDATA is enabled while LTCLK is disabled<br>This is used as a selection signal for parallel connection to another system<br>via LT bus                                                                                                                                                                         |

| <b>3</b> 9     | LTCLK            | 1   | Clock input for shift-in and shift-out of LTDATA<br>Although 8 or 16 clock pulses are handled as a unit, it is permitted to stop<br>at smaller clock pulses if performing mode change by LTCNT0 and LTCNT1<br>which resets LTCLK                                                                                                            |

| \$             | LTDATA           | 1/0 | Serial data input/output<br>LTCLK<br>LTDATA<br>(INPUT)<br>MSB<br>MSB<br>MSB<br>MSB<br>MSB<br>MSB<br>MSB<br>MSB                                                                                                                                                                                                                              |

| <b>89</b><br>Ø | LTCNT1<br>LTCNT0 | 1   | Control signal specifying the data content of LTDATA<br>LTCNT1<br>LTCNT0<br>LTDATA CBIT UBIT SETTINGS STATUS<br>Settings : Sets the internal conditions of the IC (transmit/receive, etc.)<br>Status : Monitors the internal conditions of the IC (unlock, etc.)<br>Internal counters and the like are reset at either edge of both signals |

| ¢              | SETSY            | 1   | Latch clock input for settings information sent by LTDATA LTCLK LTDATA SETTINGS SETSY UBIT Internal conditions                                                                                                                                                                                                                              |

### **DIGITAL AUDIO INTERFACE (DAI)**

| Pin No. | Name   | 1/0 | Function and timing                                                                                                                                                                                                                                                                                                             |

|---------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | IRQU   | 0   | Output signal specifying the state of the internal register that is the buffer<br>for inputting and outputting U-bit data<br>[In transmission]                                                                                                                                                                                  |

|         |        | 2   |                                                                                                                                                                                                                                                                                                                                 |

|         |        |     | LTDATA U-BIT                                                                                                                                                                                                                                                                                                                    |

|         |        |     | Data read<br>out over TX                                                                                                                                                                                                                                                                                                        |

|         |        |     | (In reception)<br>No more data to be read out over TX<br>U-bit data<br>over RX                                                                                                                                                                                                                                                  |

|         |        |     |                                                                                                                                                                                                                                                                                                                                 |

|         |        |     | LTDATA U-BIT                                                                                                                                                                                                                                                                                                                    |

|         |        |     | IRQU                                                                                                                                                                                                                                                                                                                            |

|         |        |     | Data to be read out by microcomputer has been stored in register                                                                                                                                                                                                                                                                |

| Ø       | USYNCI | 1   | Control signal specifying during transmission the timing to read out over TX<br>U data consisting of units of 8 bits and stored in the internal register                                                                                                                                                                        |

|         |        |     | USYNCI                                                                                                                                                                                                                                                                                                                          |

|         |        |     | U data<br>over TX U DATA1 U DATA2 U DATA3                                                                                                                                                                                                                                                                                       |

|         |        |     | Two kinds of timing are available to choose from by means of NOWD in<br>settings data<br>If NOWD = 0, timing is at the negative or positive-going edge of USYNCI<br>with no time delay<br>If NOWD = 1, U-bit data is transmitted at the position 4 fs words after each<br>negative-going edge of USYNCI                         |

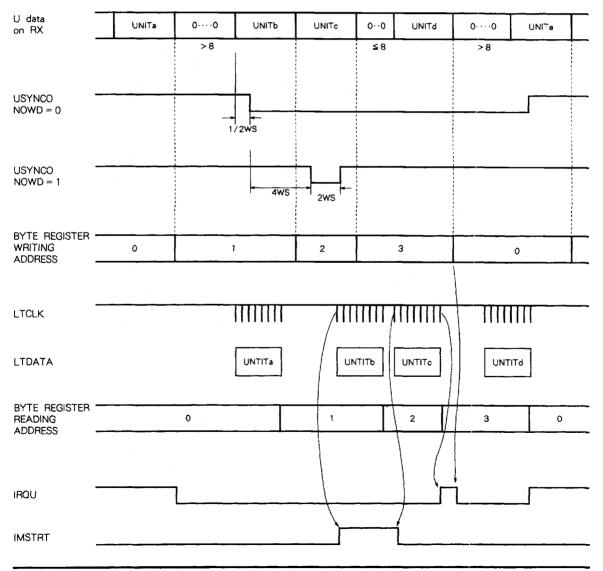

| 43      | USYNCO | 0   | Signal output indicating during reception word sink, namely, 9 bits or more consecutive "0"s in U-bit data in received RX signal                                                                                                                                                                                                |

|         |        |     | U-bit data 1 0 · · · · 0 1<br>over RX > 8                                                                                                                                                                                                                                                                                       |

|         |        |     |                                                                                                                                                                                                                                                                                                                                 |

|         |        |     | Two kinds of timing are available to choose from by means of NOWD as is<br>in the case of USYNCI<br>If NOWD = 0, USYNCO is inverted each time word sink occurs without delay<br>If NOWD = 1, USYNCO is set to "0" after a time delay of 4 fs words<br>from word sink, then set to "1" 2 fs words thereafter                     |

| 4       | IMSTRT | 0   | This signal during reception also indicates word sink similarly to USYNCO. It<br>is output in synchronization with the reading out from LTDATA of 8-bit data<br>preceding word sink<br>During transmission, it is an output signal indicating an occurrence of 9-bits<br>or more consective "0"s in U-bit data read out over TX |

### **DIGITAL AUDIO INTERFACE (DAI)**

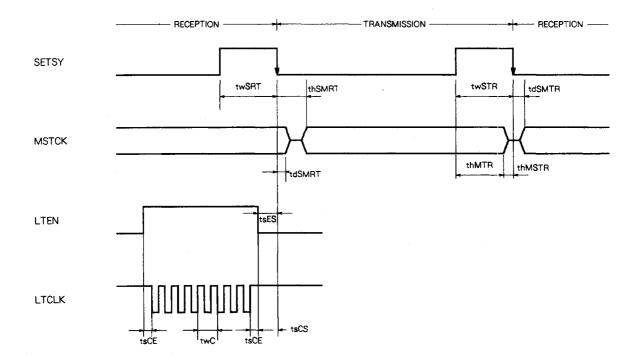

#### The timing of settings data

Eight-bit settings data inputted through LTDATA is latched by the internal register at the negative-going edge of SETSY and establishes IC operating conditions.

#### · The timing of status data

Internal operating conditions (PLL lock, etc.) are loaded into the shift register at the negative-going edge of the first bit of LTCLK. They are shifted out bit by bit at the following negative-going edges.

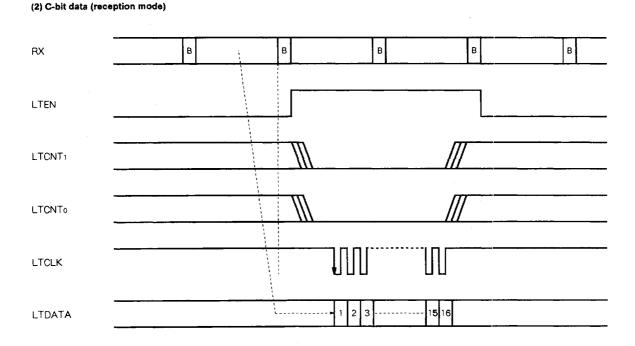

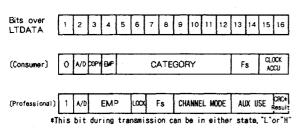

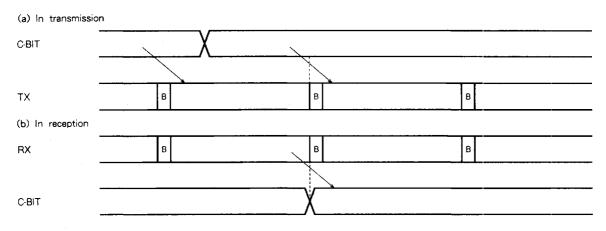

#### The timing of C bit

Channel status can be inputted to and output from a block (192 frames) in units of 16 bit. In order for C bit' during transmission to be sent over TX in such a manner that another data set is contained in another block, 16 bit of C-bit data entering the IC will be sent over TX at the beginning (the position of preamble "B") of the next block. Regarding 16 bit of data inputted as LTDATA, they will move to other latches within approximately 500ns after the 16th bit has entered, so that the next 16 bit of data can be successively inputted to the IC.

The 16 C bit contained in the previous block and held in internal latches during reception are loaded to the shift register in parallel form at the negative-going edge the first bit of LTCLK. They will be shifted out at the next negative-going edge of LTCLK.

## **DIGITAL AUDIO INTERFACE (DAI)**

3. DATA READ OUT TIMING (DAI → MICROCOMPUTER)

LATCH TIMING

### **DIGITAL AUDIO INTERFACE (DAI)**

Contents of C-bit data

#### (3) U-bit data (reception mode)

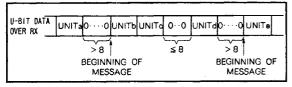

#### 1) The general form of U-bit data

The general form is suitable for the U-bit data of CD and DAT. In that form as shown in Fig. 1 one unit of U-bit data consists of 8 bits, namely, a sink bit (= 1) at the beginning plus following 7 information bits.

|    | 0     | 1 | 2 | Э      | 4     | 5   | 6 | 7 |

|----|-------|---|---|--------|-------|-----|---|---|

| [  | 1     | х | X | х      | х     | x   | x | x |

| ទា | NK BI | r |   | INFORM | ATION | BIT |   |   |

Fig. 1 U-bit data unit structure

Any number of "0"s can be inserted between units during transmission as shown in Fig. 2 If 9 or more "0"s are inserted in succession, the following unit is the start of a message. In other words, more than one units constitute a message and 9 or more "0"s separate messages.

The M51581FP in microcomputer mode is designed to interface in accordance as a rule with the general form of U-bit data.

At the reception block in particular, data is processed unit by unit assuming that U-bit data in received signals is conforming to the general form.

Fig. 2 The general transmission form of U-bit data

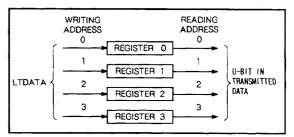

#### 2) The structure of the U-bit data registers

The U-bit data registers are 4 pieces of byte registers (8 bits), an outline of which is shown in Fig. 3 Each register has independent addresses for writing and reading data. Data is written according to LTCLK given by a microcomputer. When 8 bits of data are written, the writing address increases by one. On the other hand, data is read based on

MSTCK. In reading, one bit is allocated to a subframe in Ubit data sent over TX. When one byte of data is read, the reading address increases by one. The 4 registers are used cyclically as they are counted up.

The timing to read the first bit stored in a register is decided by the USYNCI signal.

Fig. 3 The structure of U-bit data registers

#### 3) U-Bit data timing during reception

The byte registers during reception are configured in the same way as transmission. Data is written and read based on MSTCK and LTCLK, respectively.

Received U-bit data is stored in the byte registers by information units. IRQU becomes "1" if read/write addresses coincide. This means, if IRQU is "0" new data received is written and is readable by microcomputer.

IMSTRT is "1" during the time between the start of reading the beginning unit of a message and the start of reading the next information unit. Consequently, a microcomputer during reception monitors IMSTRT, or USYNCO, which is explained later, to recognize the beginning of a message and also monitors IRQU to obtain U-bit data through LTDATA by LTCLK.

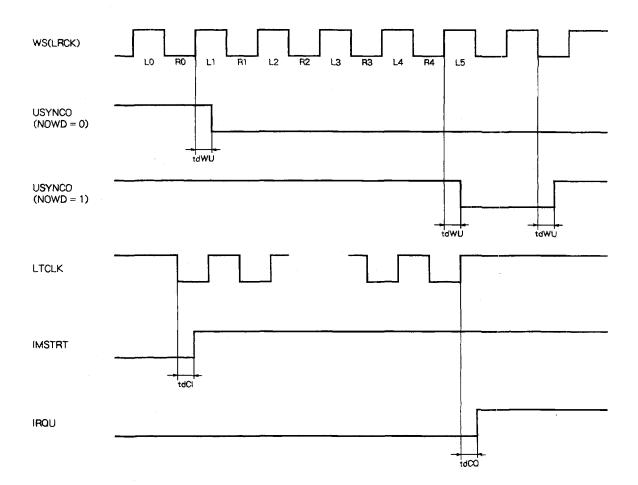

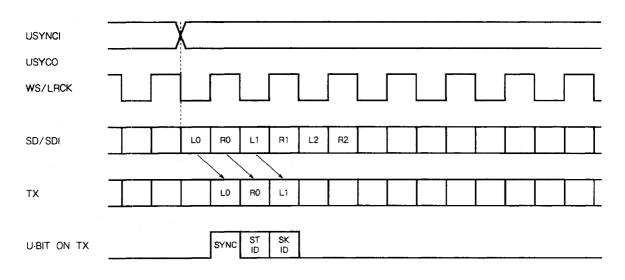

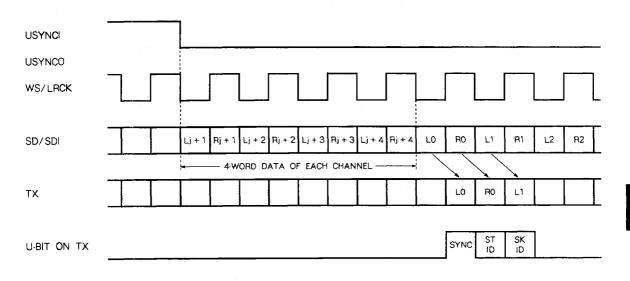

#### 4) The Timing of USYNCI, USYNCO

As each subframe contains one U-bit, there is a U-bit in every 1/2 period of the LRCK signal. In applications of the IC to R-DAT especially, transmission should be managed so that audio sampling position during one drum turn coincides a U-bit. Since the U-bit read out position is based on USYNCI as explained above, inputting the drum revolution reference signal from the signal processing IC to USYNCI satisfies the requirements for R-DAT.

However, the frequency of the reference signal and the relationship between the positions of the reference signal and audio sampling are not uniform. For this reason, the M51581FP has two modes, which can be selected by NOWD in settings data. The two modes are defined as follows.

### **DIGITAL AUDIO INTERFACE (DAI)**

#### (In transmission)

NOWD = 0

· U-bit are read at both edges of USYNCI

· Reading U-bit starts 1/2 LRCK after an edge of USYNCI NOWD = 1

- · U-bit are read at the negative-going edges of USYNCI

- Reading U-bit starts 9/2 LRCK after a negative-going edge of USYNCI

#### (In reception)

#### NOWD = 0

- The USYNCO signal is inverted at the beginning of each message

- USYNCO changes at an edge of LRCK following the sink bit of the beginning of a message

NOWD = 1

- USYNCO falls at an edge 4 LRCK after the sink bit of the beginning of a message

- ·USYNCO stays at "0" for a period of 2 LRCK

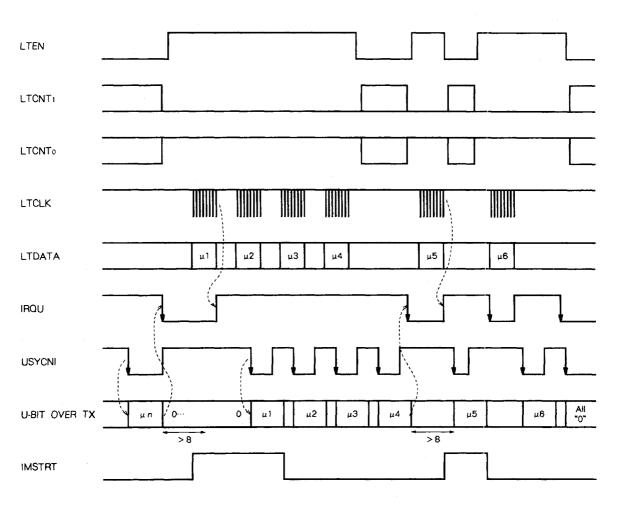

(4) U-bit data read out timing

## **DIGITAL AUDIO INTERFACE (DAI)**

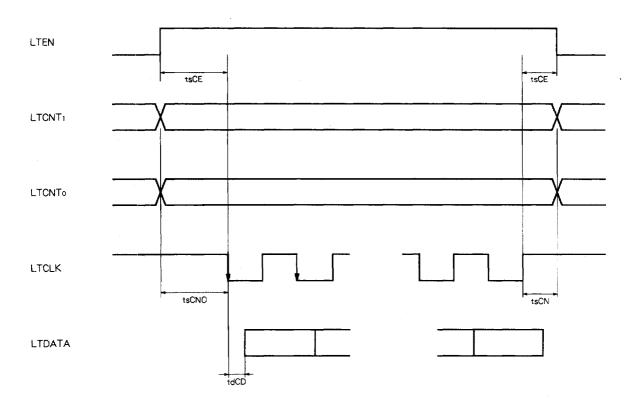

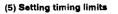

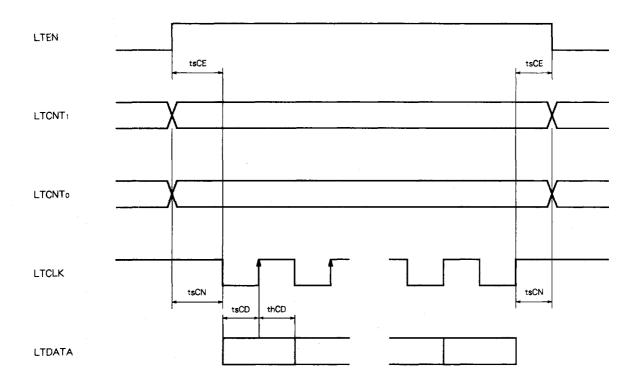

#### (5) Timing limits for reading status, C-bit data, and U-bit data

| 0      | Deventer                           |      | Unit |     |      |

|--------|------------------------------------|------|------|-----|------|

| Symbol | Parameter                          | Min  | Тур  | Max |      |

| tsCEO  | Data output LTCLK-LTEN setup time  | 1000 |      |     | nsec |

| tsCE   | LTCLK-LTEN setup time              | 50   |      |     | nsec |

| tsCNO  | Data output LTCLK-LTCNT setup time | 1000 |      |     | nsec |

| tsCN   | LTCLK-LTCNT setup time             | 50   |      |     | nsec |

| tdCD   | LTCLK-LTDATA delay time            |      |      | 250 | nsec |

Note: As internal registers for data output are set at edges of the LTEN, LTCNTO, and LTCNT1 signals, at least one of these signals must be inverted in advance to read out status, C-bit data, and U-bit data.

## **DIGITAL AUDIO INTERFACE (DAI)**

#### (6) Timing limits of usynco, IRQU, and IMSTRT

| Sumbal | Parameter               |     | Limits |     |      |  |

|--------|-------------------------|-----|--------|-----|------|--|

| Symbol | rarameter               | Min | Тур    | Max | Unit |  |

| tdWU   | WS-USYNCO delay time    |     |        | 200 | nsec |  |

| tdCi   | LTCLK-IMSTRT delay time |     |        | 150 | nsec |  |

| tdCQ   | LTCLK-IRQU delay time   |     |        | 150 | nsec |  |

**DIGITAL AUDIO INTERFACE (DAI)**

4. DATA WRITING TIMING (MICROCOMPUTER  $\rightarrow$  DAI)

(1) Setting

| SETSY                     |   |       |           | <b>_</b> |

|---------------------------|---|-------|-----------|----------|

| LTEN                      |   |       |           |          |

| LTC <b>N</b> T1           |   |       |           |          |

| LTCNTo                    |   |       |           |          |

| LTCLK                     |   |       |           |          |

| LTDATA                    |   | 1 2 3 | 4 5 6 7 8 |          |

| LSI<br>OPERATION<br>STATE | X |       |           | X,       |

| LTEN            |   |       |       |   |

|-----------------|---|-------|-------|---|

| LTCNT1          |   |       | ///   |   |

| LT <b>CNT</b> o |   |       | ///   |   |

| LTCLK           |   |       |       |   |

| LTDATA          |   | 1 2 3 | 15 16 |   |

| RX              | В | В     | B B B | В |

<sup>(2)</sup> C-bit data (transmission mode)

**MITSUBISHI SOUND PROCESSOR ICs**

## M51581FP/GP

### **DIGITAL AUDIO INTERFACE (DAI)**

#### (3) U-bit data (transmission mode)

Reading and writing the U-bit data registers are carried out in asynchronization with each other so that IRQU is used as a signal to recognize the state of the two addresses. If both addresses match, IRQU becomes "0". Since there is no more data to be transmitted (read) at this point, priority is given to writing, as a rule.

If IRQU = 0 and USYNCI falls (when NOWD = 1), transmission data will be all "0".

IMSTRT is a signal that if 9 or more continuous "0"s are found in U-bit data transmitted over TX stays at "1" until the end of reading the next 1 byte data. As data is read based on USYNCI, a gap over 9-bit or more in USYNCI lets "0"s be transmitted as data on and after the 9th bit.

As explained above, the microcomputer, while monitoring IRQU, sends U-bit data to LTDATA by LTCLK. Furthermore, it can send U-bit at any desired positions by controlling USYNCI.

The M51581FP has 4 bytes of internal registers, so it is also possible to input 4 bytes of U-bit consecutively and then transmit them other TX by controlling USYNCI.

**DIGITAL AUDIO INTERFACE (DAI)**

#### (4) The timing of USYNCI

(a) NOWD = 0

(b) NOWD = 1

### **DIGITAL AUDIO INTERFACE (DAI)**

| Sumbai | Peramotor                                         | Limit | s (Unit : | sec)     | Remark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|---------------------------------------------------|-------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | Parameter                                         | Min   | Тур       | Max      | nemark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| twSRT  | SETSY pulse width at change from R to T           | 4μ    | -         | -        | Value with an allowance considering the requirement of 4<br>clock pulses of MSTCK(128fs) in SETCY pulses and a failure<br>of low VCO oscillation frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| twSTR  | SETSY pulse width at change from T to R           | 1μ    | -         | -        | 4 clock pulses under condition of fs = 32kHz assuming that MSTCK is stably supplied during transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |