# **Technical Guide**

Vol. 31

ORDER NO. APD9401402

# **Auto DCC Technology**

AUTO PRODUCTS DIVISION

Matsushita Communication Industrial Co., Ltb

# CONTENTS

| PRINCIPELS OF THE DIGITAL COMPACT CASSETTE                            | Page  |

|-----------------------------------------------------------------------|-------|

| 1. Introduction                                                       |       |

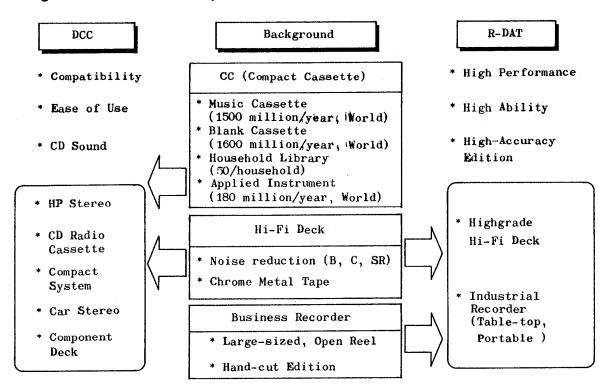

| 2. Back ground of DCC Development                                     | 2     |

| 3. Main featuers                                                      |       |

| 4. Schematic Diagram                                                  | 3     |

| 5. Block Diagram                                                      |       |

| 6. PASC System                                                        |       |

| *Principles of PASC                                                   | 0 17  |

| (1) Concept of compression-1                                          |       |

| (2) Concept of compression-2                                          |       |

| *How does the PASC operate ?                                          |       |

| *PASC s Encoding Actions                                              |       |

| Step 1. Dividing Signal into Bands by Band Pass Filter                |       |

| Step 2. Sub-Band Signal Selection and Tape Recording Bits Designation |       |

| Step 2. PASC Format of Audible Signal                                 |       |

| 7. Stationaly Thin Film Head                                          | 10.00 |

| 8. DCC Mechanism                                                      |       |

|                                                                       |       |

| 9. DCC Cassette Tape                                                  |       |

| 10. Tape Format                                                       |       |

| 11. DCC Error Correction                                              |       |

| 12. Spec                                                              | 31    |

|                                                                       |       |

| EXPLANATION OF MECHNISM                                               |       |

| 1. Mechanism Layout                                                   |       |

| 2. Loading/Eject Operation                                            |       |

| 3. Explanation of Each Mechanism                                      |       |

| 4. Mechanism Control Block                                            |       |

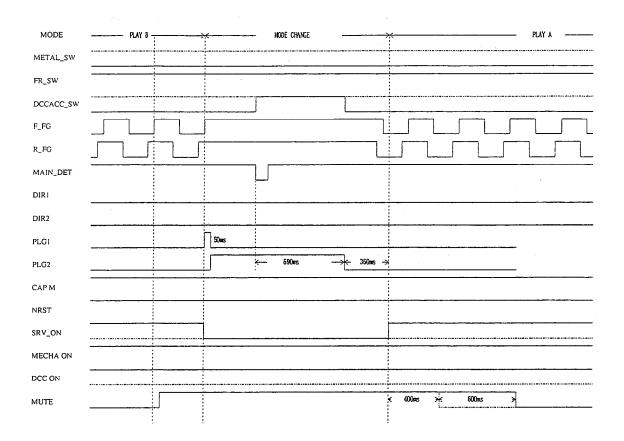

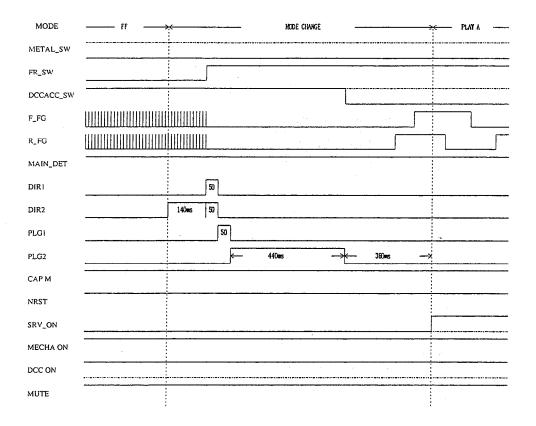

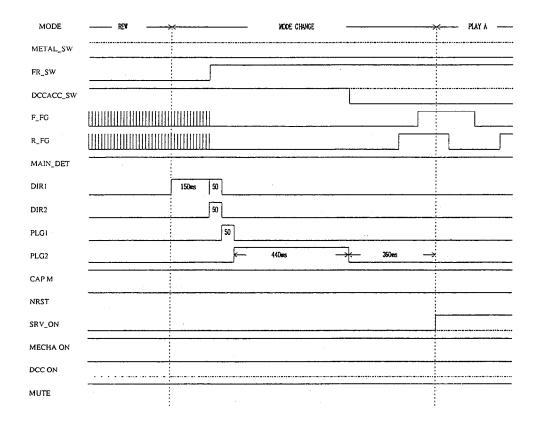

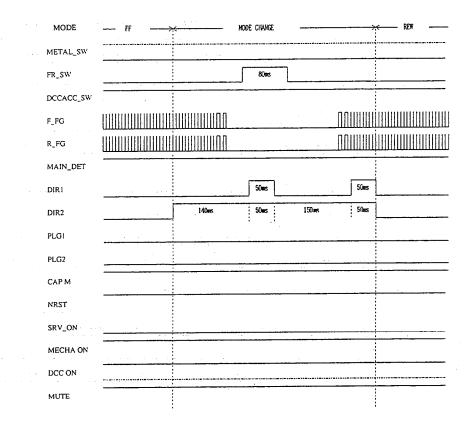

| 5. Deck Timing Chart                                                  | 47-54 |

|                                                                       |       |

| EXPRANATION OF DCC CIRCUIT                                            |       |

| 1. Flow of Signals and Function of Each Block                         | 55-56 |

| 2. Block Diagram of DCC                                               |       |

| 3. Description of Signal Name                                         |       |

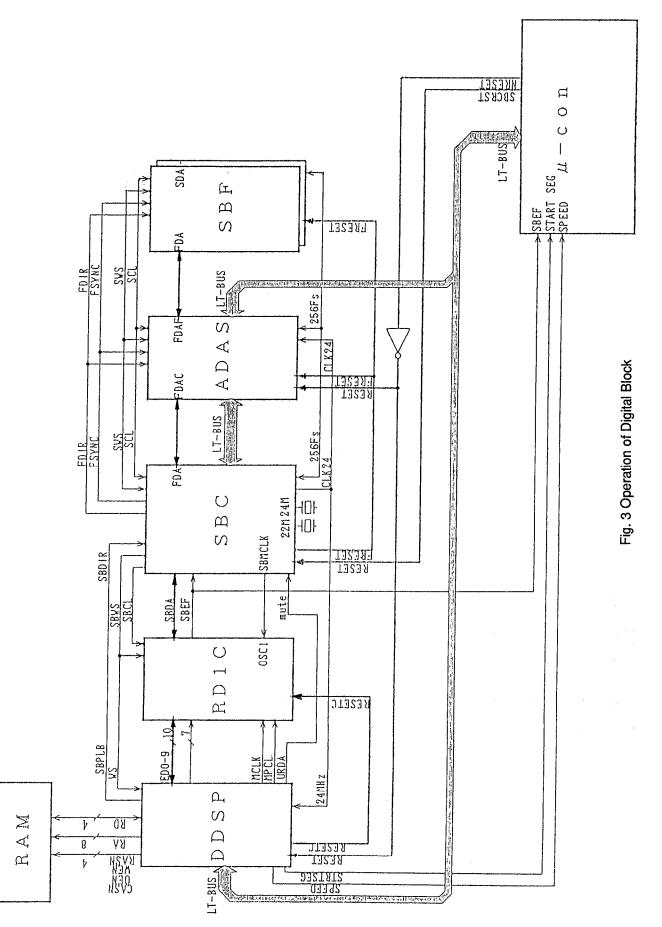

| 4. Operation of Digital Block                                         | 60-61 |

| 5. DCC Read Amplifier                                                 | 62    |

| 6. DEQ/Digital Equlizer                                               | 63-66 |

| 7. DDSP/Digital Drive Signal Processing                               | 67-69 |

| 8. ERCO/Error correctiopn                                             | 70    |

| 9. ADAS/Adptive Allocation and Scaling                                | 71-72 |

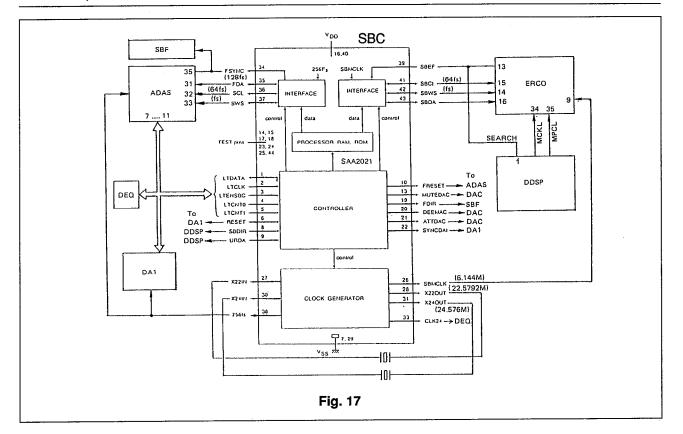

| 10. SBC/(Sub Band decoder)                                            | 73-75 |

| 11. SBF/Sub Band filter                                               | 76-77 |

| 12. D/F/Digital Filter and D/A/Digital Audio Convertor                |       |

| 13. System Control Block                                              |       |

| 14. DCC Servo Circuit                                                 |       |

| 15. DCC Seach Operation                                               |       |

|                                                                       | 00 00 |

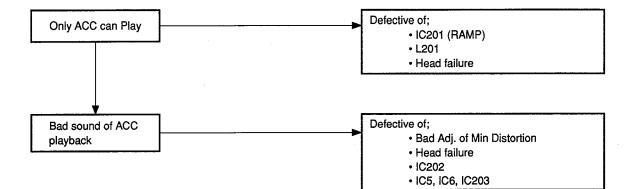

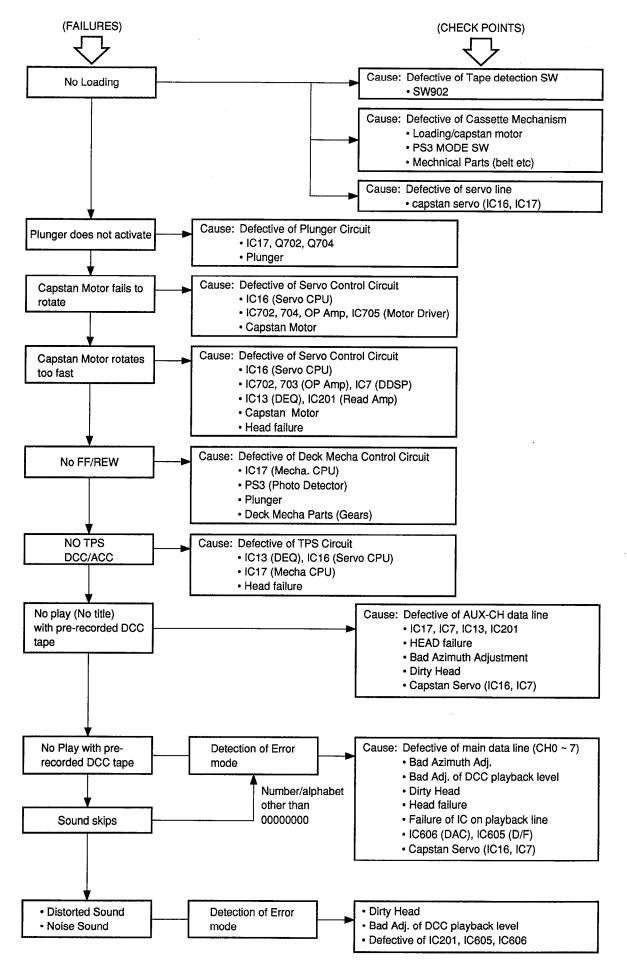

| TROUBLESHOOTING GUIDE                                                 |       |

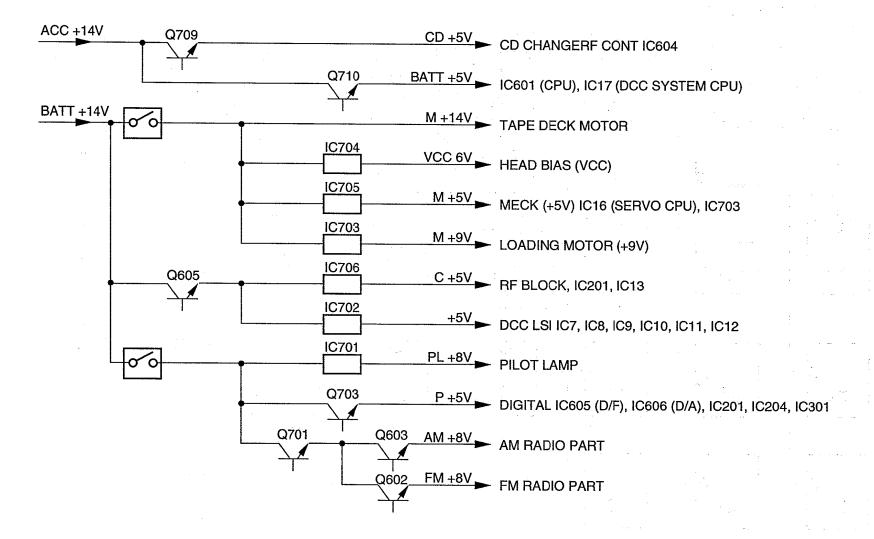

| 1. Power Supply Chart                                                 |       |

| 2. Check Points in Mechanism                                          |       |

|                                                                       |       |

| 3. Check Points in Playback                                           |       |

| 4. Check Points by Phenomenon                                         | 91-92 |

|                                                                       |       |

# PRINCEPLES OF THE DIGITAL COMPACT CASSETTE

# 1. Introduction

#### DCC – Digital Inheritor of Compact Cassette's Role in Audio Life

Music lovers learned to live with the scratches and noise of vinyl LPs for several decades. But when compact discs came along, the advantages were obvious. It was as if a veil had been removed, revealing a crispness and clarity that was previously enjoyable only at a live concert. And what about the cassette, that most popular of all audio media? After two decades of evolution that gradually reduced noise, raised headroom, and extended frequency response, audiophiles can now look forward to a true revolution. It's called the Digital Compact Cassette or DCC and it was announced by Philips N.V., of the Netherlands, at the 1991 Winter CES on January 9, 1991.

Behind this achievement are more than two years of collaborative development between Philips and Matsushita. As co-developers, we at Matsushita announced officially on July 5, 1991 that the development of basic technologies for DCC was completed, and that we were ready to provide any party interested with the license.

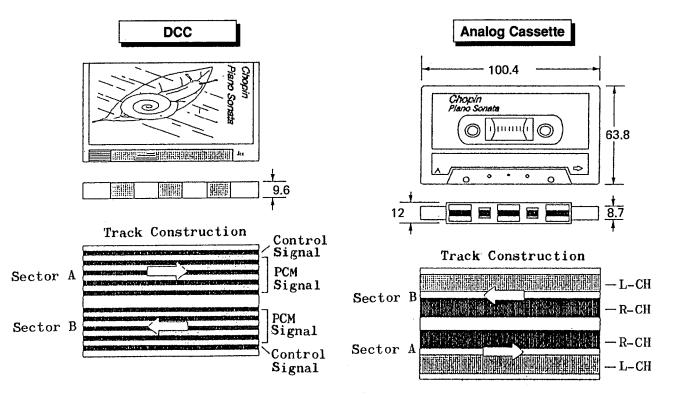

DCC is expected to inherit the role of the analog compact cassette in home audio, car audio, and personal audio applications. DCC has many of the familiar features of its predecessor, including size that matches the compact cassette. While DCC features digital sound quality and a modern high-tech look, it retains the casual convenience features that have contributed to the compact cassette's overwhelming popularity.

In fact, thanks to new technology, DCC maintains backward compatibility with analog cassettes, yet provides the sound clarity and convenient access that people have come to take for granted in today's digital formats such as the compact disc. All of this makes the DCC the most important development in audio since the compact disc was introduced eight years ago.

Support from all parts of the audio and entertainment industry is essential to the launch of a new medium. So the overwhelming cooperation of major record companies and the music industry in general augur well for DCC's success. DCC will be launched as a system. Hardware and prerecorded/blank cassettes will be available in parallel. In other words, as soon as the first DCC players and recorders are introduced, you will also have a wide and attractive array of DCC music cassette titles and blank tapes from which to choose. For these reasons we expect market penetration to surpass even that of the CD, both in terms of product quantity and rapidity of acceptance. Thanks to this new digital format's high quality sound, ease of use, and backward compatibility, the DCC revolution may prove to be one of the smoothest in audio history.

# 2. Background of DCC Development

# 3. Main Features

- (1) Compatibility with Analog Cassette

- DCC player plays analog cassette, too.

- DCC mechanism has been remodeled of currently used cassette mechanism.

- · Existing production equipment, improved, manufactures DCC music cassettes.

- (2) Up-to-date Digital Technique

- · PASC coding makes sound nearly equivalent to CD.

- Highly accurate selection of tunes by address information.

- Multi-channel stationary thin-film head.

- (3) High-technology Sense & High Additional Value

- CD-like fresh cassette design.

- · Lettering information including titles, song words, etc.

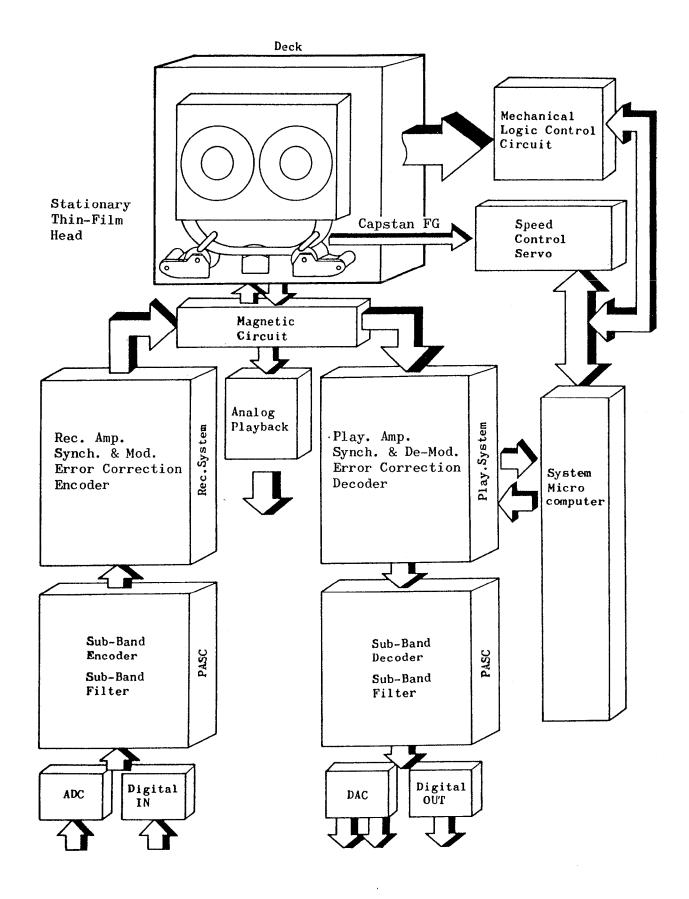

# 4. Schematic Diagram of Entire DCC

Fig. 1

- 3 -

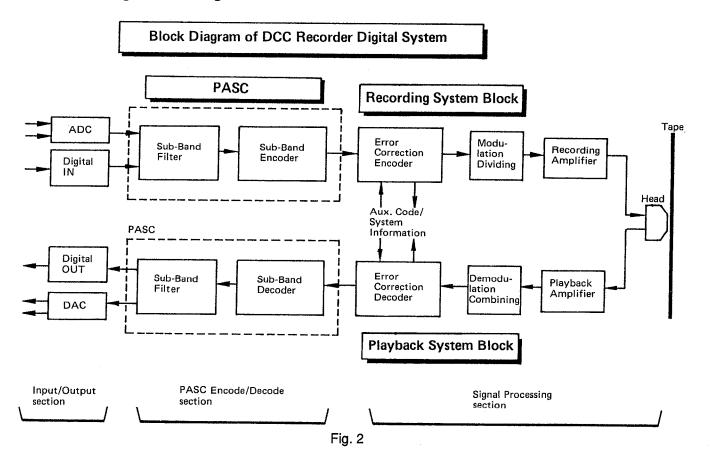

# 5. Block Diagram and Signal Flow

Compressing data and recording on channel B:

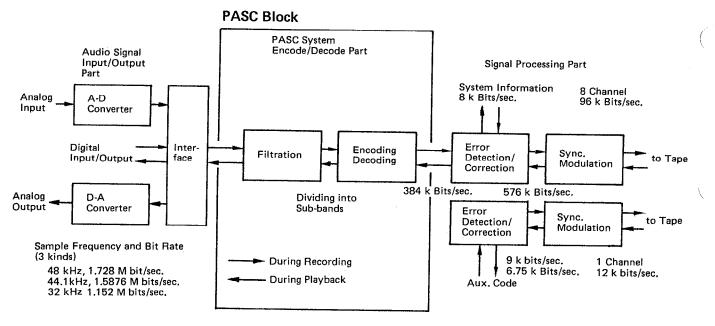

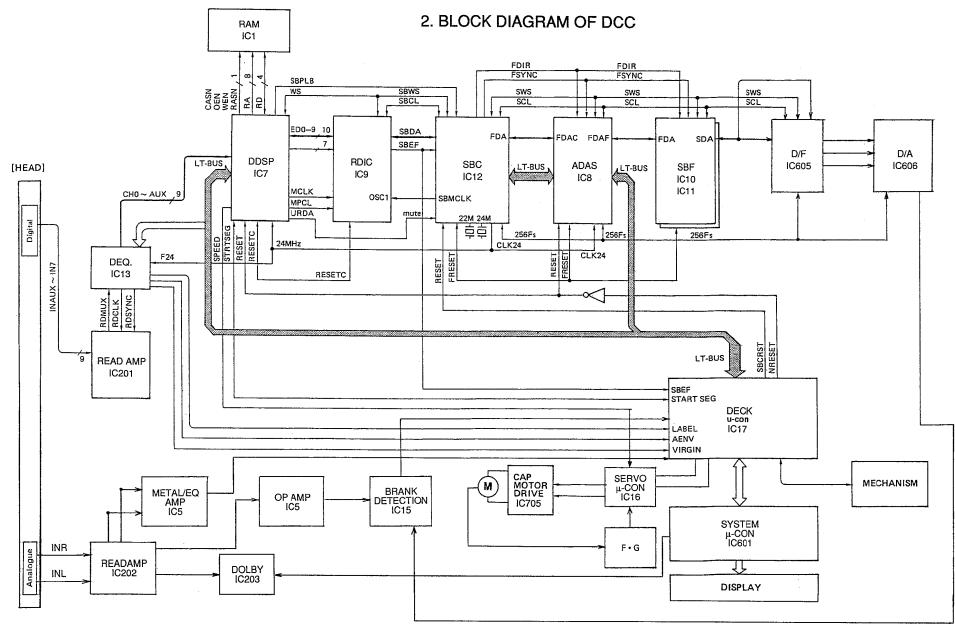

Fig. 2 is a block diagram showing the circuit of the DCC recorder, which can be roughly divided into three components, namely Audio Signal Input/Output Section, PASC Encode/Decode Section, and Signal Processing Section.

Input/Output Part consists of A-D converter, D-A converter, and digital/audio interface circuit. Encode/ Decode Part uses sub-band filters for coding, and highly efficient encoder and decoder.

Signal Processing Part comprises those circuits that are used for error detection and correction, for synchronization and synchronism detection, and for modulation and demodulation.

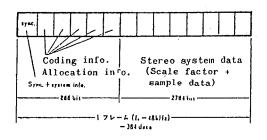

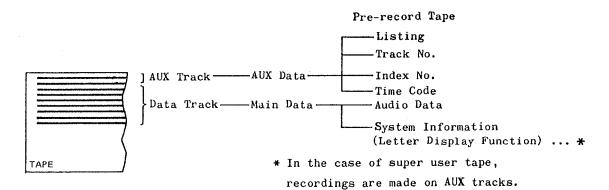

There are three kinds of digital signals recorded on tape and played back. They are audio signal, auxiliary code (data to control heading, etc.), and system information.

Recording and playback signals are generally processed as follows:

For recording, analog or digital input signals are divided into sub-bands, and encoded in the PASC method. To the encoded signals, error detecting/correcting signals are added. These data are divided into eight and recorded on 8 tracks simultaneously. Modulation is 8-10 conversion.

For playback, signals from tape are amplified, equalized, and then demodulated (10-8 conversion). Thereafter, errors, if any, are detected and corrected. The signals are demodulated in the PASC method. The data is output in the form of digital or analog signals.

# 6. PASC System

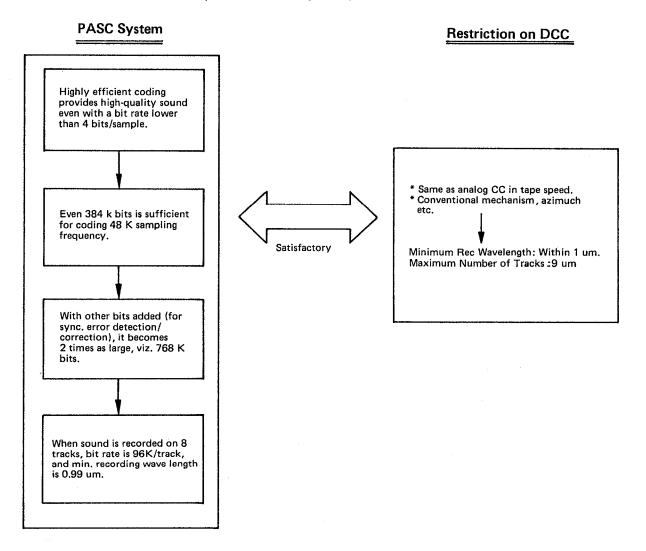

1. PASC (Precision Adaptive Sub-band Coding) Principles

Why is PASC requisite? ..... Because the bit rate of recording signal is restricted when it is necessary to provide interchangeability with the existing system as a feature of the DCC.

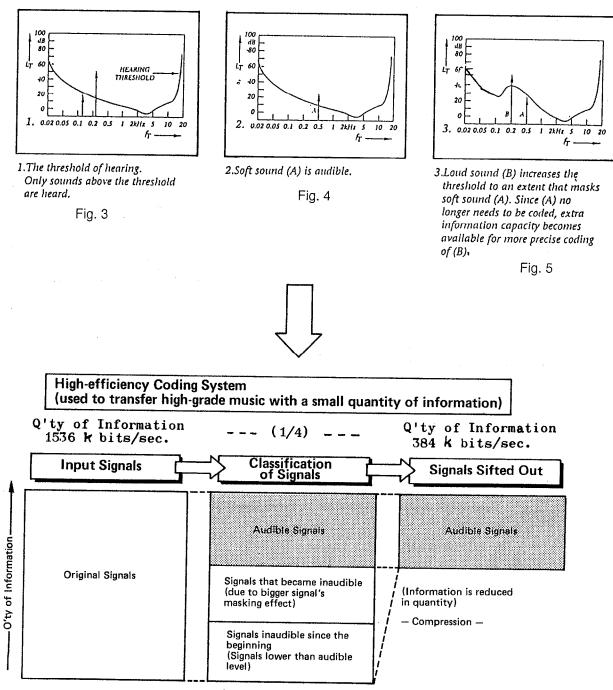

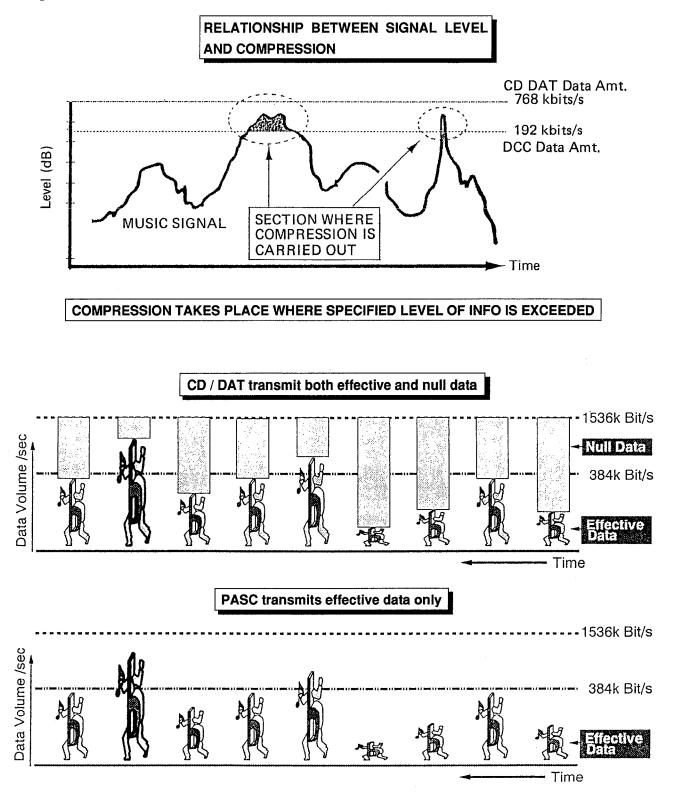

#### Principles of Compression

- 1. Man is hearing sound higher than a certain level.

- 2. Bigger sound masks smaller ones.

- 3. Music signals do not range to entire bands.

OK if you record at a level higher than the detection limit only.

{ You need not record evenly.

{ Data is concentrated to necessary part.

(Psychological sound analysis)

In regard to actual music signals, the amount of digital data is ordinarily such as to enable recording on a tape without the process of compression, but data compression is necessary for only those sections where the amount of digital data is too much as shown below.

In each section where data has to be compressed, music signals centering round hardly-audible part are thinned

to such an extent that almost no difference from original signal can be perceived by man's auditory sense. (Compression Process)

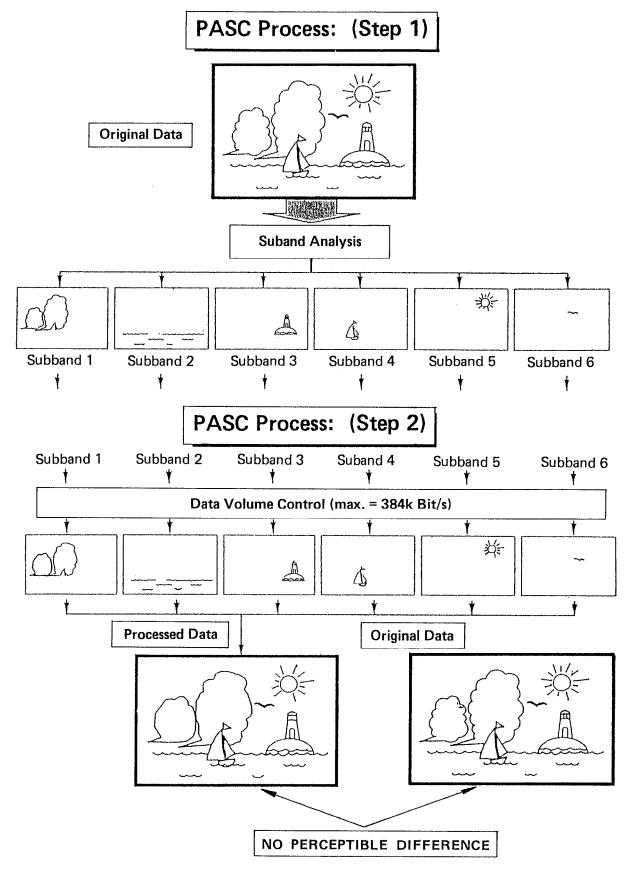

Given below is an example showing that the picture taken by a camera (via. after compression) does not differ perceptibly from the actual scene (original sound.)

# (2) CONCEPT OF COMPRESSION-2

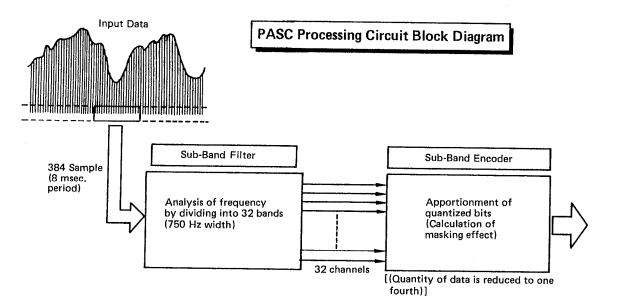

# How does the PASC operate?

- 1. Frequency is divided into 32 bands through the digital filter.

- 2. Signal processor codes audible sounds only on the basis of auditory detection limit.

- 3. Capacity bits are apportioned to sub-bands, and unnecessary bits of any band are sub-divided to other bands as required.

Fig. 8

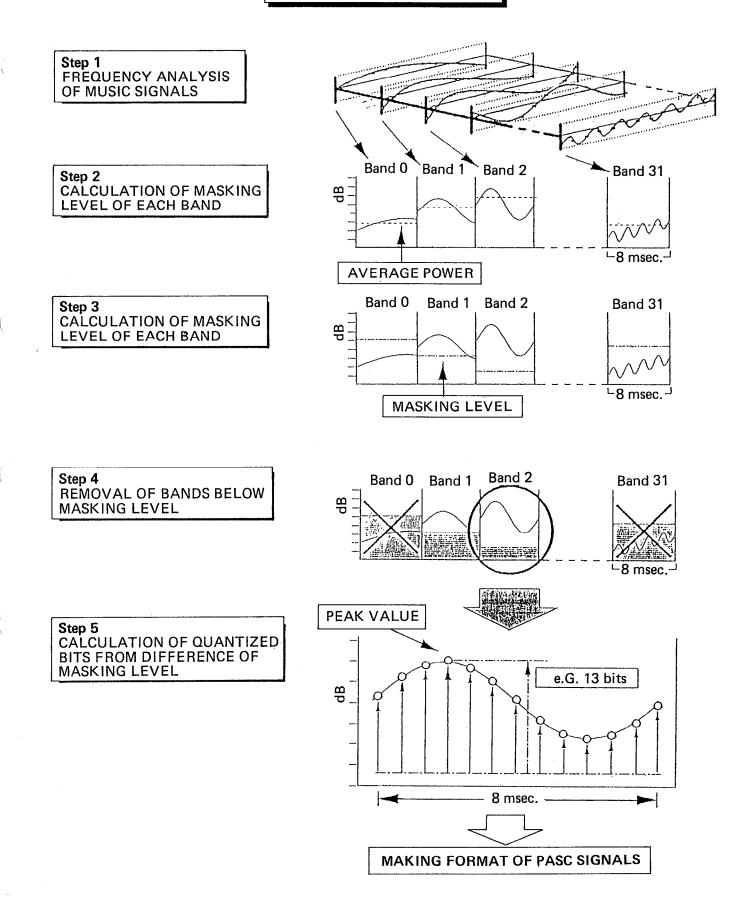

## PASC'S ENCODING ACTIONS

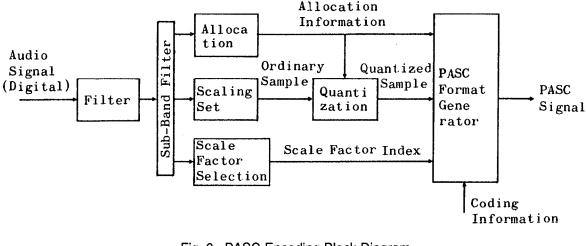

Fig. 3 shows a block diagram of PASC operation during a recording time. Every audio signal is digitalized before entering the PASC.

Fig. 9 PASC Encoding Block Diagram

## STEP 1. DIVIDING SIGNALS INTO BANDS BY BAND-PASS FILTER

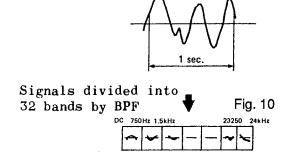

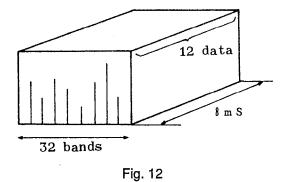

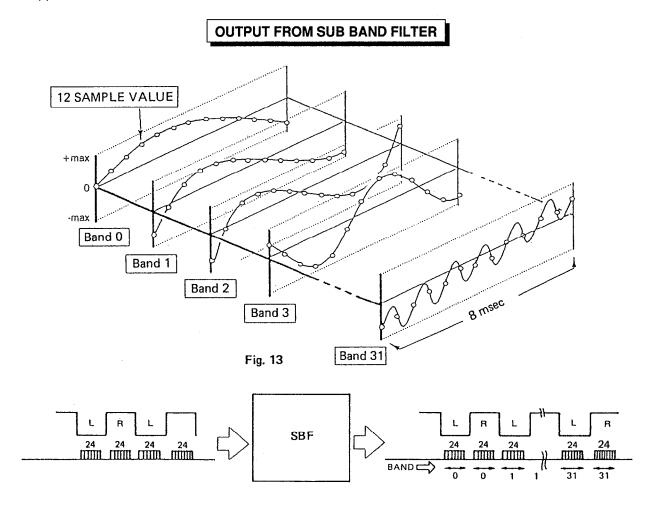

Audio signals, quantized and input, are first divided into 32 bands as they pass through the FIR digital SBF (SBF = Sub-Band Filter).

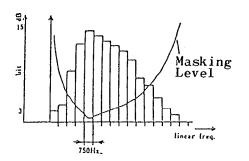

In the case of sampling frequency 48 kHz, for instance,  $48 \div 2$  $\div 32 = 750$  Hz forms a BPF band. With signals bearing an audio band between 20 Hz ~ 48 kHz, it can be expressed that audio signals have been divided into 32 sub-bands of 750 Hz.

Fig. 10 Shows the pattern analogically.

As mentioned above, audio signals have been digitalized

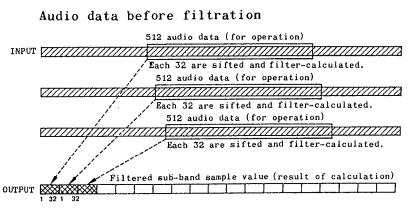

before being filtered actually. Through matrix operation, 32 sub-band signals can be determined continuously. 512 data out of continuous input signals are taken in, operated, and then each 32 audio data are moved and let through filtration.

At the time of filtration, signals on the input side of SBF IC are 16 ~ 18 bit digital signals and those on the output side are 24 bit, more finely quantized than input signals. The state of operation with regard to the above is pictured to the right.

Fig. 11

32 data obtained through operation are drawn up in due order from low to high frequency bands. If lower ones from the lowest are collected in the time-axis direction,  $0 \sim 750$  Hz band signal data will be obtained. Groups of data having been divided by SBF are arranged by sub-bands, and every time the number of sub-band data comes up to 12, the data are processed as 1 unit. In short, 32 sub-bands × 12 data = 384 data reprocessed as a unit.

In the case of 48 kHz sampling frequency,  $384 \times 1/48,000 = 8$  m sec is PASC's signal processing unit time.

That is to say, PASC continues to process signals at a rate of 125 times/sec as long as audio signals are supplied.

(

#### STEP 2. SUB-BAND SIGNAL SELECTION AND TAPE-RECORDING BITS DESIGNATION

<Determination whether audible or inaudible to human's car>

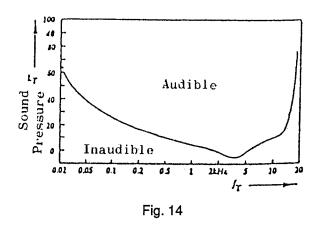

To determine it, the following masking theory is adopted.

- Human's audible level curve dependant on frequencies

- · Masking effect by surrounding noises

- Regarding each sub-band in STEP 2,

- Whether the data is audible to human's year or not (Whether it should be tape-recorded or not), and

2. How many bits when recording.

These are decided immediately and simultaneously.

#### <Allocation of quantized bits to audible signals>

Output from SBF is 24-bit data as mentioned before. Recording this data as it is does not lead to highefficiency coding. Thinning it evenly into 10-bit data will result in conspicuous deterioration of sound quality and listeners will recognize it as a strange sound easily.

Since the audio data transfer rate of PASC is 384 k bits/sec (cf. ordinary coding requires 1.536 k bits), limited bits should be apportioned effectively. For this purpose, PASC uses some rules. Typical ones of which are as follows:

(1) Apportionment of bits to suit for human's auditory characteristics, and

(2) Apportionment of bits depending on audible signal level.

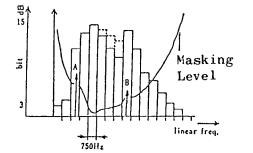

In the case of (1), the sub-band covering the frequency to which human's year is sensitive is alloted big quantized bits, and other sub-bands smaller bits, as is manifest from the auditory characteristics shown in Fig. 14.

The borderline curve (hearing threshold) where sound is barely audible or inaudible differs depending on individuals. For PASC, a curve with a margin applicable to very sensitive persons has been set.

In the case of (2), the number of bits is determined in proportion as signal protrudes from the audibility curve shown in Fig. 14.

Exemplified below is how the number of quantized bits is assigned to the same band with a few examples concerning the cases of (1) and (2) above.

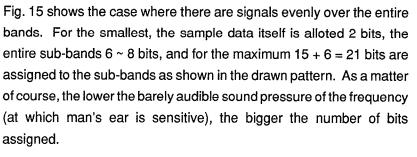

Fig. 16 shows the case where only A and B are high in sound pressure. Sub-band 2 where sound A is located is alloted 10 or more bits (generally  $5 \sim 6$  bits). Consequently bits of other sub-bands are cut as shown by broken lines. But this has no influence upon the auditory sense since there has been no sound.

If the level of A is higher as shown in Fig. 17, PASC assigns 21 bits (the maximum number of bits) to this sub-band.

As explained above, this part of signal processing by PASC has been so designed as to act according to a very flexible logic.

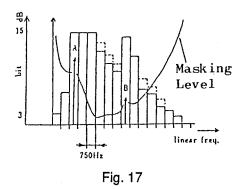

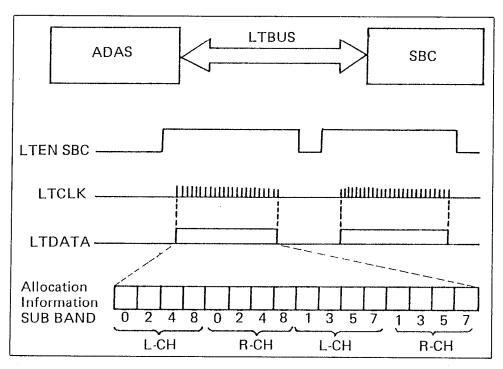

<Allocation Information>

The number of bits alloted to each band is transferred as allocation information by 4-bit binary code to the next stage (SBC). This is an expression with 4 bits through comparison of the peak of each signal with the masking level as shown below.

#### STEP 3. PASC FORMAT OF AUDIBLE SIGNAL

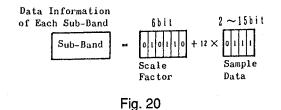

Through steps 1 and 2, signals to be recorded on the tape have been determined. Next step is to arrange these signals to the PASC format in compliance with the DCC standard. Used for this purpose are IC called SBC (Sub-Band Coding), etc.

This value (the maximum value of each sub-band) is called a 'scale factor.'

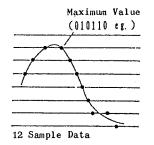

As mentioned above, 12 data are housed in each sub-band. Fig. 19 shows the state as viewed analogically. (Digital data on the practical side)

In the PASC format, the maximum value is detected out of 12 data, and it is quantized by 6 bits for 32 subbands evenly.

This maximum value represented by 6 bits is called a 'scale factor.'

In the next place, the 12 data are quantized with the number of bits (one of 2 ~ 15 bits). Fig. 20 shows the state.

$12 \text{ samples} \times 24 \text{ bits} = 288 \text{ data bits per sub-band}$ . This data, if audible, goes through PASC coding and the number of bits gets between the following minimum and the maximum:

Minimum  $-6 + 12 \times 2 = 30$  bits

Maximum -  $6 + 12 \times 15 = 186$  bits

Actually PASC signal is completed with coding information including (1) sub-band No. ,(2) number of quantized bits of this sub-band, etc added to it. (see Fig. 21)

Fig. 21 PASC Data Format

To supplement Step 3, the following explains the meanings of 'scale factor' and each sample data.

<Scale Factor>

Due to quantization over the entire audio bands by use of the same scale, the scale factor determines the dynamic range. In short, the scale factor indicates the ratio of the level of the signals housed in a sub-band to the entire audio signals.

| Output |         | Scale  |                                             |

|--------|---------|--------|---------------------------------------------|

| Level  |         | Factor |                                             |

| +5dB   | <u></u> | 000000 |                                             |

| +4dB   |         | 000001 |                                             |

| +2dB   |         | 000010 | The scale factor is weighted by 2 dB for a  |

|        |         |        | 1 bit of change and, therefore, the dynamic |

|        |         |        | range of DCC is 6 bits = 124 dB.            |

|        |         |        |                                             |

| -116dB |         | 111101 |                                             |

| -118dB |         | 111110 |                                             |

|        | Fig. 22 |        |                                             |

<Quantized Bits>

The number of quantized bits given to each sub-band is equivalent to the S/N ratio. If the number of the bits is small, it is detected as a quantized noise depending on frequencies. If it is quantized with maximum 15 bits,  $15 \times 6 + 2 = 92$  dB will become the S/N of DCC.

## <Scale Factor and Its Relations>

Providing there is a value X = 23487, this value is expressed in the case of PASC as follows:  $X = 10^5 \times 0.23487$ .

The index of '5' is equivalent to the scale factor, and indicated by 6 bits as '000101.' Depending on the number of quantized bits determined by the sub-band in which the value is housed, the 0.23487 varies, for instance, to become 0.235 or 0.23 as sufficient.

(Example)

For 5-bit expression of X = 23487,

Index part: 000101

Mantissa part: 10111 (= 23)

If the sub-band to which this value belongs is important, it is turned into PASC data by use of 15 bits, Index part: 000101 (unchanged)

Mantissa part: 101101110111111.

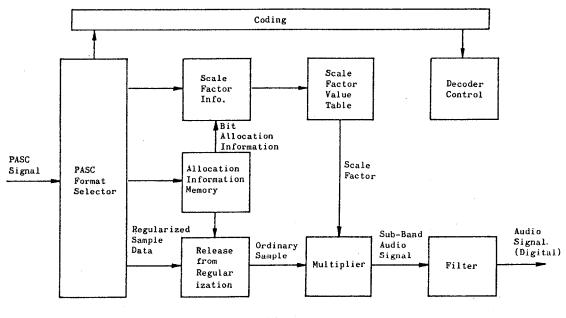

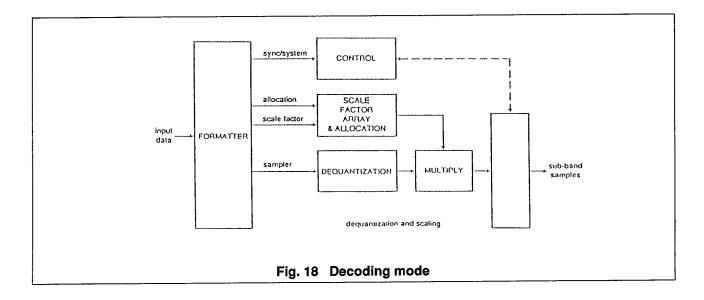

#### PSC'S DECODING (SIGNAL REGENERATING) ACTIONS

Fig. 23 is a block diagram showing actions of PASC during decoding.

The flow is fundamentally in reverse order of encoding. Signals read out of the head are waveform-shaped, returned into 8-bit unit data through  $10 \rightarrow 8$  demodulation, and then undergoing error-correction, they are returned into PASC format data, that is, they are classified as follows:

- Which sub-band

- Number of scale factors

- Bits at quantization

- Inport of 12 data

The data are returned into 12-point data of maximum 32 batches per 8 ms. At this time, according to coding information or allocation information, the signal wave form of each sub-band is returned into a waveform of correct amplitude by use of scale factor.

Thereafter, these are subjected to multiplication to be signals covering the entire audio bands.

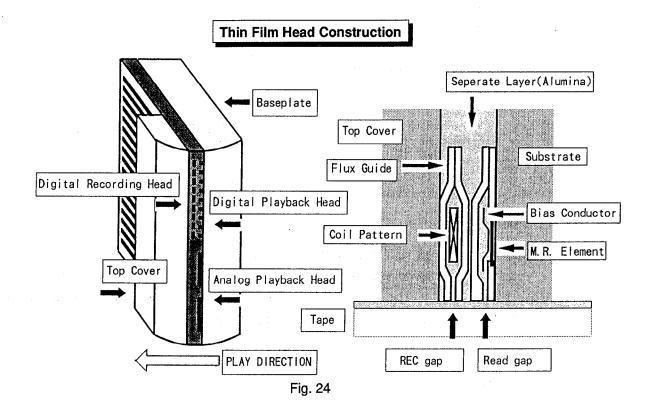

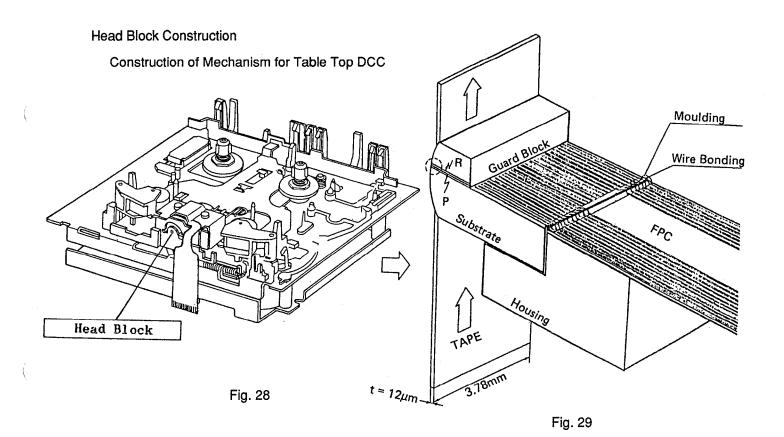

# 7. Stationary Thin-Film Head Construction

Stationary thin-film head, which excels in integral density, is produced in making products low-priced and uniform in quality. Also, sharp formation of magnetic field and advantageously high saturated magnetic flux density help us improve the recording density greatly.

As compared with the conventional heads, it is less expensive for the number of tracks due to smaller interstices between tracks (narrower guard bands).

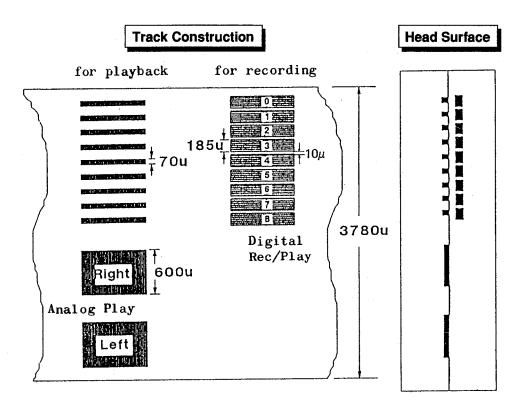

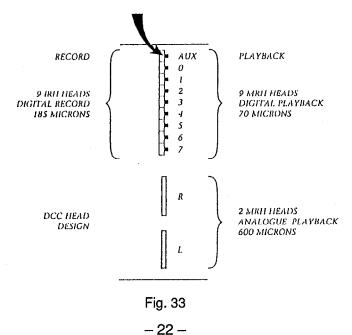

The DCC system required new type thin-film heads to be designed, and three kinds of heads are combined at present. The recording head used to record digital audio signals has 9 Integrated Recording Heads (IRH) in it. Besides, there are 9 Magneto-Resistive Heads (MRH) used for playback of the digital signals, and 2 Magneto-Resistive Heads (MRH) used for playback of analog audio signals.

Fig. 25

Digital audio heads are located on one side (half) of the head part, and audio analog heads are on the other side (half).

Therefore, the direction of a DCC tape running in the recording mode is reverse to that of the tape running in a compact cassette during recording.

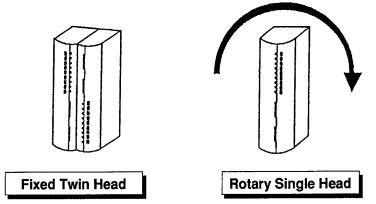

A portable type DCC uses 2 fixed heads overlaid one on the other but in opposite directions. In the case of a table top DCC and car DCC, a rotary head is used, for selection of either sector A or sector B of the tape used.

Digital signals are recorded on 9 parallel tracks. (Track Pitch = 195  $\mu$ m, Track Width = 185  $\mu$ m)

The playback head width is  $70 \,\mu$ m. The reason why the head width has been made narrow is that deterioration of playback signals caused by azimuth angular deviation should be minimized even when the head gap is inclined during recording. Deterioration is thus smaller than in the case of a compact cassette.

#### Comparison with analog cassette

As shown on page 20, DCC's digital signals are on the upper side of sector A of the tape running in the recording/playback mode, whereas ACC's are on the lower side contrary to the conventional concept of sectors A and B.

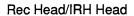

Recording current of about 0.15A is applied in pulse mode.

Unlike analog, this pulse record is used to reduce recording current.

Shown below are construction of actually used thin-film part, and the state of recording on tape. According to channel bits input, magnetization takes place by inverse characteristics as shown below.

Fig. 30

Fig. 31

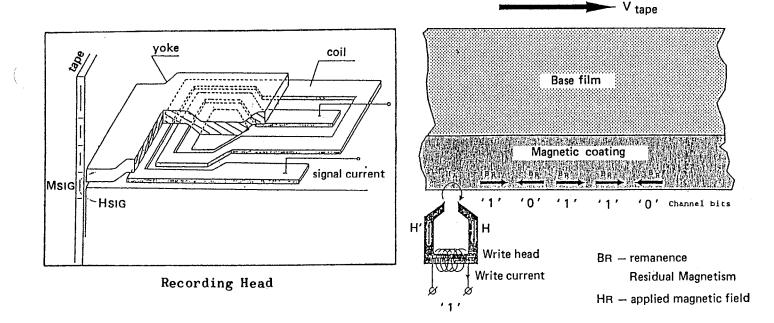

In an integrated recording head, the signal current conductor is surrounded by a flux guide which concentrates the magnetic field into the recording gap in conventional fashion. The MRH playback head, on the other hand, features an advanced magneto-resistive element whose resistance varies with the magnetic field impressed on it from the tape, via the flux guide. A constant current is fed through the element, so that the voltage across it varies with the magnetic field on the tape.

Magneto-resistive heads are excellent for reading DCC bit transition.

For analogue playback, the high stability and absence of noise and hystereiss of magneto-resistive heads also ensure top quality. At the same time, the inherently high bit rate capability allows for a wide frequency response.

The head face has a thin anti-wear coating; continuous tape travel across the head causes no damage.

# 8. DCC Mechanism

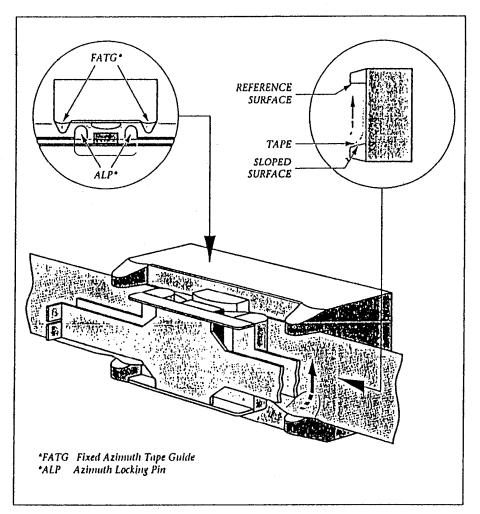

One brand-new feature of the DCC cassette is the two Azimuth Locking Pins (ALPs). In conjunction with the Fixed Azimuth Tape Guidance (FATG) mechanism fitted to the head assembly, the ALPs ensure not only improved tape-head contact, but also consistently repeatable alignment of the tracks on the tape with the heads.

The ALPs increase the wrap-around angle of the tape against the head. This extends the tape-head contact area and optimizes the physical conditions for signal recording and reading. The tape is also stiffened in this crucial tape guidance area, and this contributes to the high accuracy of the FATG mechanism.

In the FATG mechanism, special slots are mounted on either side of the head assembly. The two top edges of the slots form reference surfaces to align the tape with the head. Meanwhile, the sloping profiles of the lower parts of the slots gently force the stiffened tape upwards against both reference surfaces. For all practical purposes, this simple device eliminates azimuth error.

The ALPs/FATG design requires no complicated mechanisms or close tolerances. Its very simplicity ensures permanently accurate tape-head alignment.

Tape-head engagement: optimal wrap-around with the ALPs (inset) and azimuth alignment with the FATG (inset)

Fig. 34

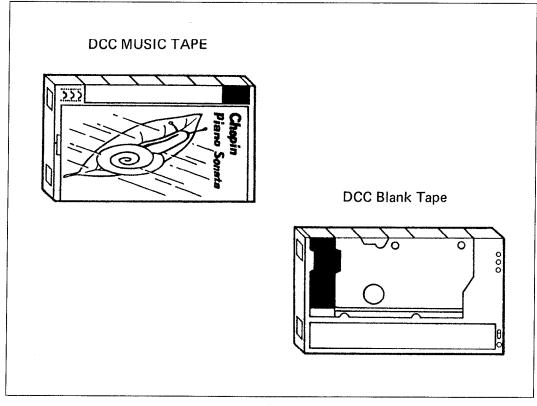

# 9. DCC Cassette Tape

The DCC cassette is a Compact Cassette with a difference. It has the same basic dimensions, records on forward and reverse tracks, and uses (video) chrome or equivalent tape. Modern technology, however, has produced a much improved design. Both the new cassette and its holder are more stylish and more convenient.

The cassette body is also made thinner overall, because the record/playback head is more compact.

New materials are used in the DCC cassette itself. They are specified for use over a wider temperature range than the Compact Cassette.

The normally exposed tape, and the tape drive wheels, are covered by a slider. This provides the tape with built-in protection against soiling and scratches. It also locks the tape reels to solve an old problem of the cassette medium; in a DCC cassette there is little chance for the tape to unwind, get into a tangle, and then become jammed. When the cassette is loaded, the slider is automatically pushed aside. Thanks to this device, cassettes can safely be carried around without their houlders. So not only is the cassette more attractive vicually, it is also easier to pick up and use in all applications and it takes up less storage space.

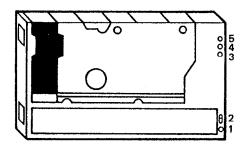

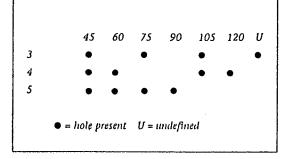

The length of a blank DCC cassette can be indicated by holes in the rear of the housing.

These enable DCC decks to calculate and display the remaining recording time.

Accidental overwriting can be prevented by a record protection switch.

DCC Blank Tape

Purpose of each hole

HOLE

- 1. Detection of DCC/ACC

- 2. Protection of error erace.

- 3. Tape Playing Times (Min.)

- 4. Tape Playing Times (Min.)

- 5. Tape Playing Times (Min.)

Tape playing times.

DCC MUSIC TAPE

A : Slider for tape protection B : Label C : Hole for Automatic Loading

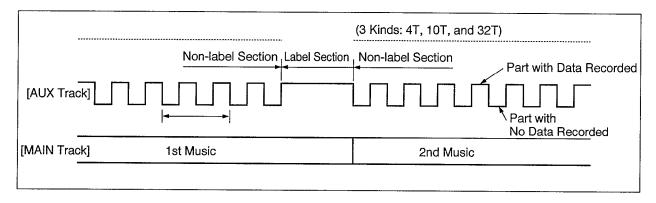

# 10. Tape Format

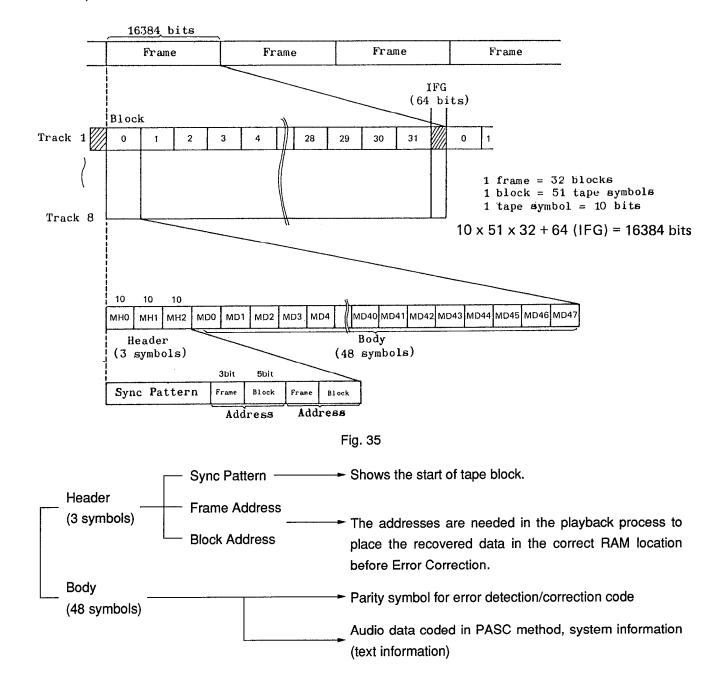

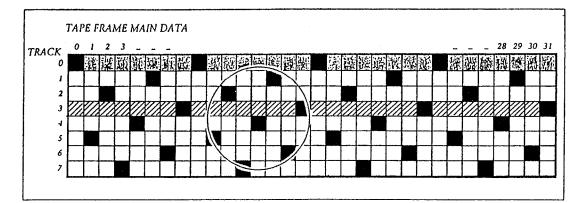

1) Main Data Format

## • IFG (Inter-Frame Gap)

The signals recorded on tape can be divided into Tape Frames. Between Tape Frames an Inter Frame Gap (IFG) with variable length is provided, to accomodate for small deviations (such as clock jitter) from the sampling frequency used during recording. Its nominal length is 64 bit periods, corresponding to about 0.4% of the nominal Tape Frame length (including IFG) of 16384 bit periods. The IFG carries a signal that has alternating polarity at every bit position.

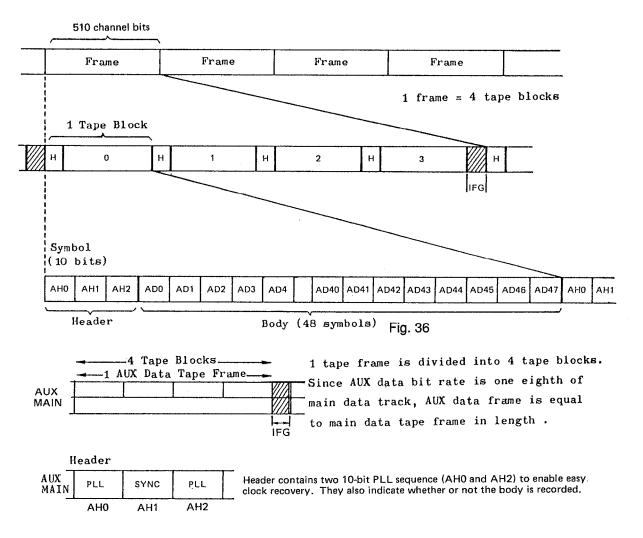

## 2) AUX Data Format

# Body Body information is repeated in each of 4 tape blocks of tape frame, and includes information given below.

|    | MSB                      |              |                      |         |        |         |          | LSB |

|----|--------------------------|--------------|----------------------|---------|--------|---------|----------|-----|

| AD | 7                        | 6            | 5                    | 4       | 3      | 2       | 1        | 0   |

| 0  | 0                        | 0            | 0                    | 0       | CC     | NTROL   | INFO     | ]   |

| 1  |                          |              | MAI                  | KER D   | 1FO    |         |          |     |

| 2  |                          | TRACK NUMBER |                      |         |        |         |          |     |

| 3  |                          |              | INDEX                | NO. / C | HAPTER | NO.     |          |     |

| 4  | SCT                      | ABS          | .FRAME               | 3       | SOB    | ABS.I   | HOUR un  | its |

| 5  | ABS MIN.tens             |              |                      |         | ABS    | .MIN.ur | nits     |     |

| 6  | ABS                      | SEC ter      | C tens ABS.SEC units |         |        |         |          |     |

| 7  | PAU                      | TR.          | FRAME                |         | RES    | TR.H    | OUR unit | s   |

| 8  | TR.MIN.tens TR.MIN.units |              |                      |         |        |         |          |     |

| 9  | TR.SEC.tens TR.SEC.units |              |                      |         |        |         |          |     |

| 10 |                          | 1            | first TOO            | C ITEM  |        |         |          |     |

| 11 |                          |              |                      |         |        |         |          |     |

| 12 | 11                       |              |                      |         |        |         |          |     |

| 13 |                          |              |                      |         |        |         |          |     |

| 14 |                          |              |                      |         |        |         |          |     |

| 15 | second TOC ITEM          |              |                      |         |        |         |          |     |

| 16 |                          |              |                      |         |        |         |          |     |

| 17 |                          |              |                      |         |        |         |          |     |

| 18 | ,,                                      |  |

|----|-----------------------------------------|--|

| 19 | ۶)                                      |  |

| 20 | ADDITIONAL INFO SPECIFIER               |  |

| 21 | · · · · · · · · · · · · · · · · · · ·   |  |

| 22 | · · · · · · · · · · · · · · · · · · ·   |  |

| 23 |                                         |  |

| 24 |                                         |  |

| 25 |                                         |  |

| 26 | *************************************** |  |

| .7 |                                         |  |

| .8 |                                         |  |

| 9  |                                         |  |

| 0  |                                         |  |

| 1  |                                         |  |

| 2  |                                         |  |

| 3  |                                         |  |

| 4  |                                         |  |

| 5  |                                         |  |

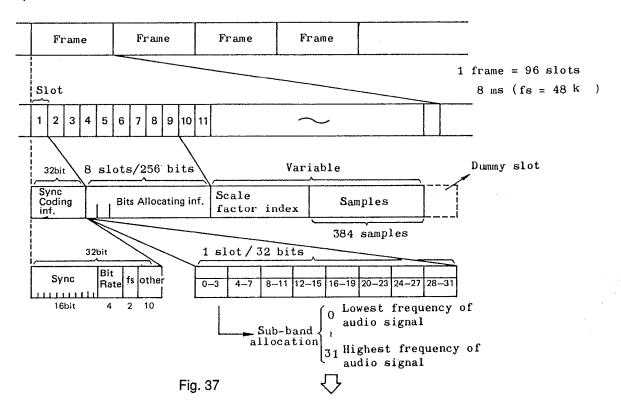

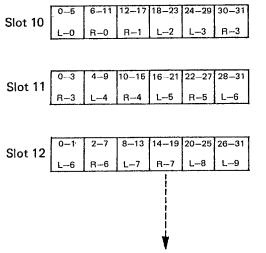

#### 3) PASC Frame Format

#### Scale factor index

For every subband where samples are transfered, a scale factor index must be transfered.

In stereo mode the allocation units must be sent in the following order:

| Slot 2: |      |       |       |         |       | فنكاله والالالف والمتعوي |      |

|---------|------|-------|-------|---------|-------|--------------------------|------|

| 03      | 47   | 811   | 12 15 | 16 19   | 20 23 | 24 27                    | 2831 |

| L-0     | R-0  | L-1   | R-1   | L-2     | R-2   | L-3                      | R-3  |

| Slot 3: |      |       |       |         |       |                          |      |

| 03      | 47   | 811   | 1215  | 1619    | 20 23 | 24 27                    | 2831 |

| L-4     | R-4  | L-5   | R-5   | L-6     | R-6   | L-7                      | R-7  |

| Slot 4: |      |       |       |         |       |                          |      |

| 03      | 47   | 8.,11 | 1215  | 1619    | 20 23 | 24 27                    | 2831 |

| L-8     | R-8  | L-9   | R-9   | L-10    | R-10  | L-11                     | R-11 |

| Slot 5: |      |       |       |         |       |                          |      |

| 03      | 47   | 811   | 12 15 | 1619    | 20 23 | 24 27                    | 2831 |

| L-12    | R-12 | L-13  | R-13  | L-14    | R-14  | L-15                     | R-15 |

| Slot 6; |      |       |       |         |       |                          |      |

| 03      | 47   | 811   | 1215  | 1619    | 2023  | 24 27                    | 2831 |

| L-16    | R-16 | L-17  | R-17  | L-18    | R-18  | L-19                     | R-19 |

| Slot 7: |      |       |       |         |       |                          |      |

| 03      | 47   | 811   | 1215  | 16 . 19 | 20 23 | 24 27                    | 2831 |

| L-20    | R-20 | L-21  | R-21  | L-22    | R-22  | L-23                     | R-23 |

| Slot 8: |      |       |       |         |       |                          |      |

| 03      | 47   | 811   | 12 15 | 1619    | 2023  | 24 27                    | 2831 |

| L-24    | R-24 | L-25  | R-25  | L-26    | R-26  | L-27                     | R-27 |

| Slot 9: |      |       |       |         |       |                          |      |

| 03      | 47   | 8.:11 | 1215  | 1619    | 20 23 | 24 27                    | 2831 |

| L-28    | R-28 | L-29  | R-29  | L-30    | R-30  | L-31                     | R-31 |

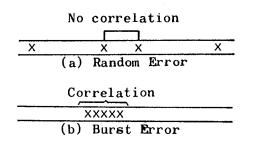

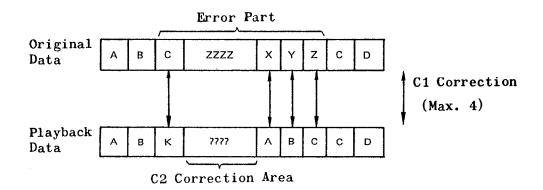

## **11. DCC Error Correction**

Errors, roughly classified, are random errors (caused mainly by noise component contained in signal) and burst errors (occurring continuously from defect or scars of tape or caused by failure of synchronism).

Random Error and Burst Error

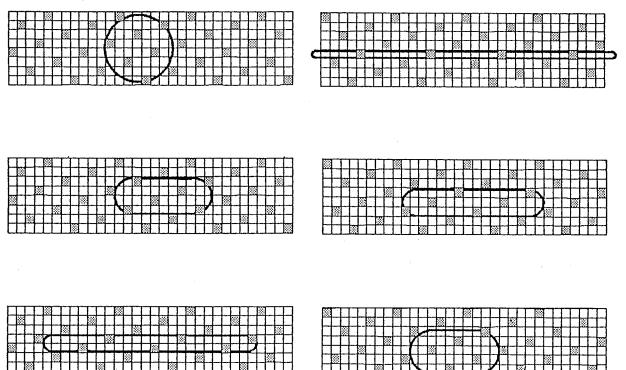

A Cross Interleaved Reed Solomon Code is employed to protect the data against random and burst errors. During playback a first code (called C1) is evaluated to detect and - if possible - correct errors within a Tape Block. As the C1 code may correct at maximum 4 error symbols per Tape Block, any errors that can Cannot be corrected are passed to the second (called C2) correction phase as erasures : indicating the location of the erroneous symbol, but not the error value.

At maximum the C2 code can correct 6 of these erasure symbols per code word. The distribution of the symbols for a C2 code word is such that an almost optimum physical distance between the symbols is achieved, resulting in a "chequer-board" pattern. This enables correction of drop outs with a diameter of up to 1.45 mm. The system can even operate if a complete track is missing, although in this case a long drop out in the other tracks is more likely to cause audible sound degradation.

The PASC bytes are distributed onto the tracks in such a way that any failure of the error correction system does not disrupt consecutive PASC bytes: an uncorrectable C1 or C2 code word will not result into a burst error in the PASC signal. This helps the PASC processor to conceal these errors.

PASC data bytes in chequer-board pattern in a tape frame. Adrop out as large as the outline shown does not impair sound quality, nor does the absence of a complete track.

Fig. 38

The area enclosed by 6 C2 symbols in the drawing can be corrected.

Lost part in the area enclosed by 6 C2 symbols in the drawing can be corrected.

|                             | DCC                                                                                   | R–DAT                 | CD                                     |

|-----------------------------|---------------------------------------------------------------------------------------|-----------------------|----------------------------------------|

| Number of Channels          | Stereo (2 channels)                                                                   |                       | ←                                      |

| Frequency Range             | fs = 48 kHz 8 ~ 22,000 Hz<br>fs = 44.1 kHz 5 ~ 20,000 Hz<br>fs = 32 kHz 5 ~ 14,500 Hz | ←                     | 20 ~ 20000 Hz                          |

| Dynamic Range               | >105 dB                                                                               | 90 ~ 94 dB            | >90 dB                                 |

| THD (+N)                    | <0.0025%                                                                              | <0.05%                | 0.0022%                                |

| Wow & Flutter               | Crystal Oscillator Accuracy                                                           |                       | <del> (</del>                          |

| <signal format=""></signal> |                                                                                       |                       |                                        |

| Sampling Frequeny           | 48, 44.1, 32 kHz                                                                      | 48, 44.1, 32 kHz      | 44.1 kHz                               |

| Coding                      | PASC                                                                                  |                       |                                        |

| Audio Bit Rate              | 384 k bits/s                                                                          | 2.46 Mbit/s           | 2.0338 Mbit/s                          |

| Error Correction Method     | C1, C2 Reed Solomon                                                                   | C1, C2 Reed Solomon   | C1, C2 Reed Solomon                    |

| Modulation Method           | 8–10 Modulation (ETM)                                                                 | 8–10 Modulation (ETM) | 8–14 Modulation (EFM)                  |

| Preemphasis                 | Option                                                                                | ← _                   | ←                                      |

| <cassette></cassette>       |                                                                                       |                       | •                                      |

| Recording Time              | D90: $45 \times 2 = 90$ min.<br>D120: $60 \times 2 = 120$ min.                        | 120 min.              | 60 min. ~ (Disc)                       |

| Таре                        | Cr Tape                                                                               | Metal Tape            | · ···································· |

| Tape Width                  | 3.78 mm                                                                               | 3.81 mm               |                                        |

| Tape Speed                  | 4.76 cm/s                                                                             | 0.815 cm/s            | 1.2 ~ 1.4 m/s (CLV/Disc)               |

| Number of Tracks            | 8 Digital Audio 1 AUX Cord                                                            | Helical Scan Method   |                                        |

| Track Width                 | 185 µm                                                                                | 2.613 mm              | 0.5 μm (pit)                           |

| Track Pitch                 | 195 µm                                                                                | 13.591 μm             | 1.6 µm                                 |

# 12. DCC vs. DAT/CD Format, and Performance Comparison

# EXPLANATION OF MECHANISM

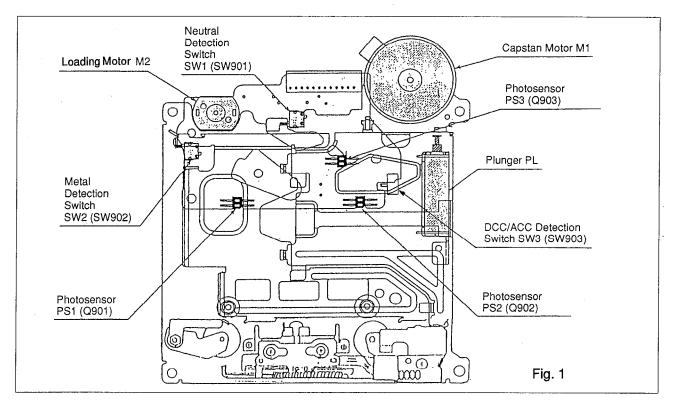

# 1. Mechanism Layout

## Functions of actuators and sensors

| Symbol<br>(No. in PCB) | Part Name                  | Function                                                |  |

|------------------------|----------------------------|---------------------------------------------------------|--|

| M1                     | Capstan Motor              | 1) Capstan and reel table rotation                      |  |

|                        |                            | 2) Mode change drive source                             |  |

| M2                     | Loading Motor              | 1) Cassette tape loading and ejection                   |  |

|                        |                            | 2) FF, Rew (incl. TPS) selection                        |  |

| PL                     | Plunger                    | 1) Trigger for mode change                              |  |

|                        |                            | 2) Fwd/Rev play direction change                        |  |

| PS1 (Q901)             | R-side reel table rotation | 1) Detection of R-side reel table rotation and rotating |  |

|                        | detecting photosensor      | speed                                                   |  |

| PS2 (Q902)             | F-side reel table rotation | 1) Detection of F-side reel table rotation and rotating |  |

|                        | detecting photosensor      | speed                                                   |  |

| PS3 (Q903)             | Main gear position         | 1) Change of mode through detection of main gear stop   |  |

|                        | detecting photosensor      | position                                                |  |

| SW1 (SW901)            | Neutral detection switch   | 1) Detection of sub-gear position for FF/REW change     |  |

|                        |                            | 2) Detection of end of loading or of ejecting action    |  |

| SW2 (SW902)            | Metal detection switch     | 1) Normal/Metal tape discrimination                     |  |

|                        |                            | 2) Detection of start of tape loading                   |  |

| SW3 (SW903)            | DCC/ACC detection switch   | 1) Detection of DCC/ACC                                 |  |

|                        |                            | 2) ACC tape H                                           |  |

|                        | ,                          | DCC tape L                                              |  |

# 2. Loading/Eject Operation

#### (1) LOADING OPERATION

#### (2) EJECT OPERATION

| MODE    | PLAY                                                              | EJECT                                                   | EJECT END              | PULL OUT                                                    |

|---------|-------------------------------------------------------------------|---------------------------------------------------------|------------------------|-------------------------------------------------------------|

| SENSORS | Press EJECT BUTTON<br>(SW 5)                                      | T-PLAY<br>(SW 901) OFF                                  | T-LOAD<br>(SW 902) OFF | <br> |

| CONTROL | MOTOR<br>CAP OFF                                                  | LOADING MOTOR                                           | Q606 OFF               |                                                             |

| REMARKS | The tape loading motor turns ON then the capstan motor turns OFF. | backward.<br>The cassette tape rises with the carriage. | forward.               | Eject Operation is completed.                               |

# 3. Explanation of Each Mechanism

# 1. Mode Change Mechanism (Main Gear Rotating Mechanism)

# 1–1. Functions of main gear

The main gear has the following functions:

- 1. Change of mode

- 2. In-Out movements of head baseplate

- 3. Rotation of playback head

- 4. Change of power motor drive force transfer route

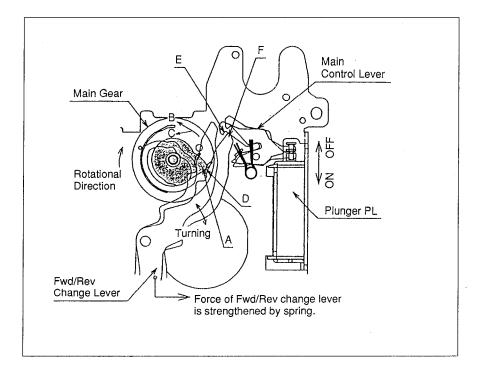

# 1-1-1. Change of mode (see Fig. 2)

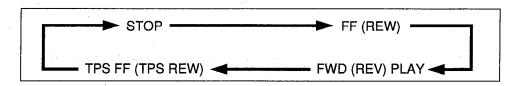

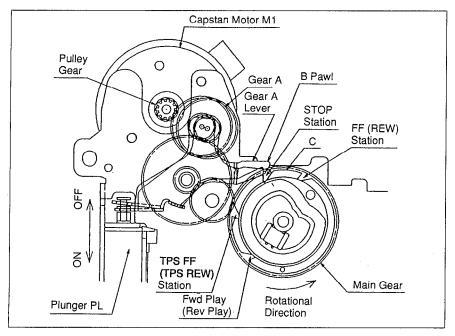

There are four notches along the outer circumference of the main gear. When pawl B of gear A lever comes to one of the notches, the main gear stops rotation. The four notches are called Mode stations. As the main gear rotates, the mode station changes in the following order repeatedly.

PS3 is used to detect the main gear's position. This sensor turns ON at the STOP position only. (see Fig.

1)

# Explanation of movements

- (1) When plunger PL is set to ON during rotation of capstan motor M1, gear A meshes with the gear of the pulley on the capstan motor M1 to rotate the main gear.

- (2) Even though plunger PL turns OFF, gear A lever's pawl B remains on part C of the main gear, so that the pulley gear is kept in mesh with gear A to rotate the main gear up to the next Mode station.

- (3) Upon arrival at the mode station, the gears are disengaged and the main gear stops.

# Fig. 2 Main gear's mode change mechanism

## 1-1-2. In-Out movements of head baseplate

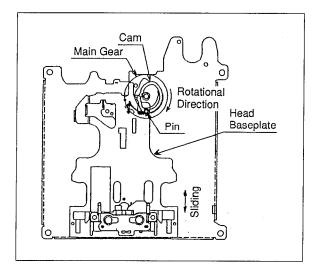

The main gear's cam meshing with the pin mounted to the head baseplate, one rotation of the main gear causes the head baseplate to move In-Out once. (see Fig. 3)

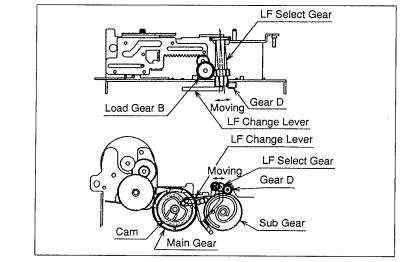

## 1-1-3. Rotation of playback head

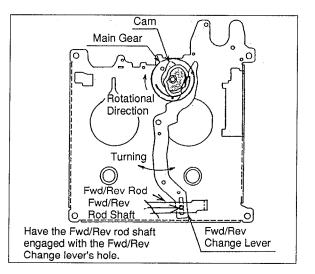

The main gear's cam, turning the Fwd/Rev change lever, causes the rotary mechanism of the head to move. (For detail, refer to Section of 'Fwd/Rev Play Change Mechanism.') (see Fig. 4)

Fig. 3 In-Out movements of head baseplate

## 1-1-4. Change of power motor drive force transfer route

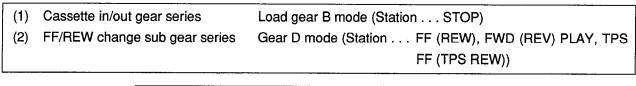

The main gear's cam, turning the LF change lever to move the LF select gear, changes the LF Select gear position to mesh between gear B and gear D. (see Fig. 5) There are two routes as follows:

Fig. 5 Change of power motor drive force transfer route

#### 2. FF/REW Mechanism

When the main gear is positioned at FF (REW) or TPS FF (TPS REW) station, the LF select gear is engaged with gear D. Then the sub gear is rotated by the power motor through gear D. (see Fig. 5)

As shown in Fig. 6, the sub gear has a spiral-shaped cam, which turns the FF lever to make the FF gear mesh with the Fwd reel table gear and Fwd flywheel gear or with the Rev reel table gear and Rev flywheel gear, thereby placing the unit into the FF or REW mode.

A, B, and C (shown in Fig. 6) of the sub gear cam are NEUTRAL, FF, and REW positions respectively.

Neutral detection switch SW1 (SW901) is used for detection of the sub-gear position. <u>This switch turns OFF</u> only when the position is NEUTRAL. (see Fig. 1)

For FF or REW, time required for turning the cam from the NEUTRAL position is about 150 ms in either direction from when the switch is turned ON.

Fig. 6 FF/REW Mechanism

#### 3. Fwd/Rev Play Change Mechanism

While the main gear is rotating from the FF (REW) position to the PLAY position, the Fwd/Rev play direction is to be changed.

#### 3-1. Fwd/Rev change lever movement

- (1) On the way from the FF (REW) mode station to the PLAY mode station the main gear causes the A-part of the cam to move the guide part D of the Fwd/Rev change lever to the right. (see Fig. 7)

- (2) If the plunger PL is at OFF position, the main control lever is at CCW-turned position. This lever is positioned according to ON-OFF of the plunger. At this time, the main control lever's pawl part E engages with the Fwd/Rev change lever's end part F. When the main gear rotates further, the Fwd/Rev change lever's guide part D moves toward the B direction of the cam. (FF)

- (3) In relation to (1) above, if the plunger is at ON position, the main control lever's pawl part E will not get engage with the Fwd/Rev change lever's end part F. When the main gear rotates further, the Fwd/Rev change lever's guide part D moves toward the C direction. (REW)

- Thus immediately after the Fwd/Rev change lever's guide part D passes the A-part of the main gear cam, the Fwd/Rev change lever changes in position according to ON-OFF of the plunger, so the unit is placed into the Fwd or Rev play mode.

## Fig. 7 Fwd/Rev change lever movement

## 3-2. Fwd/Rev rod movement

## 3-2-1. Functions of Fwd/Rev rod

The Fwd/Rev rod has the following functions:

- 1. Pressing the used-side pressure roller against the capstan.

- 2. Keeping the supply-side reel table gear from getting engaged.

- 3. Rotating the head.

## 3-2-1-1. Pressing the used-side pressure roller against the capstan

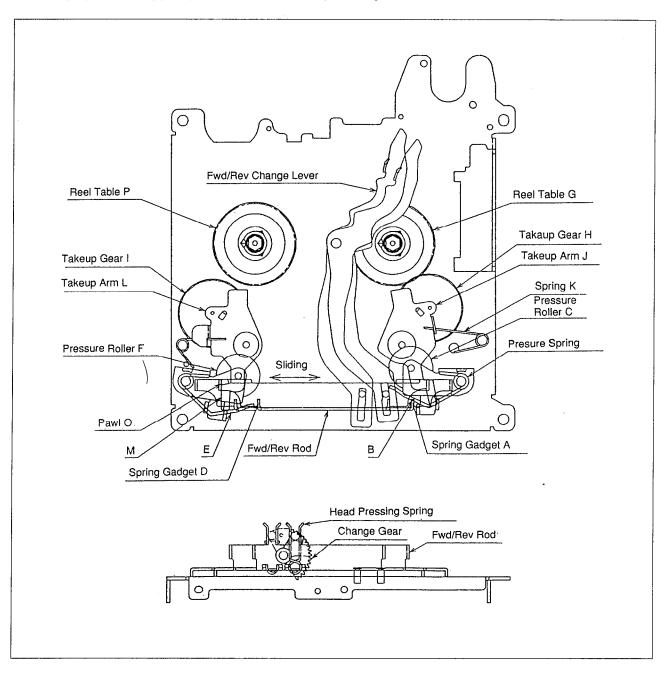

As shown in Fig. 8, the Fwd/Rev change lever makes Fwd/Rev rod slide to right or left, thereby controlling the pressure roller's position.

In the case of Fwd play, for instance, the Fwd/Rev rod slides to the right and causes the spring gadget A to press the B-part of the Fwd-side pressure roller pressing spring until the Fwd-side pressure roller C is pressed against the capstan.

At this time, the Rev-side pressure roller F is not pressed against the capstan since the Rev-side spring gadget D does not get engaged with the E-part of the Rev-side pressure roller pressing spring.

The same applies to Rev play. But, in this case, all is reverse since the Fwd/Rev rod slides to the left.

## 3-2-1-2. Keeping the supply-side reel table gear from getting engaged

As shown in Fig. 8, when the takeup gear is engaged with the gear of the reel table, the takeup gear transfers rotation from the flywheel to rotate the reel table.

For Fwd play, the takeup gear H is made to mesh with the gear of the right-side reel table G and the left-side takeup gear I is kept from meshing.

For Fwd play, as shown in Fig. 8, the right-side takeup arm J meshes with the gear of the reel table G by the force of the spring K. On the other hand, the left-side takeup arm L is held at the lower end part M by the Fwd/ Rev rod's pawl 0, and the takeup gear I is kept from meshing with the gear of the reel table P.

The same applies to Rev play. But, in this case, all is reverse since the Fwd/Rev rod slides to the left, and the left-side take up gear I meshes with the gear of the reel table P, while the right-side takeup gear H is kept from meshing.

## 3-2-1-3. Rotating the head

By making the Fwd/Rev rod sliding to right or left, the head pressing spring mounted on the Fwd/Rev rod turns the change gear rotating jointly with the head, thereby causing the head to rotate.

Fig. 8 Fwd/Rev rod movement

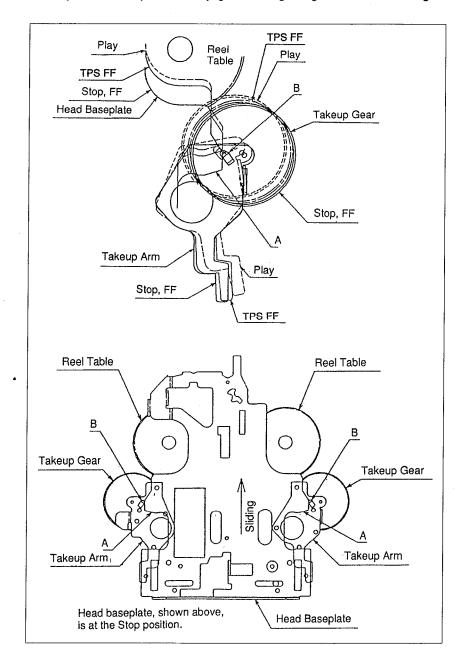

## 3-3. Takeup gear meshing control (Functions of head baseplate)

Besides the above-mentioned Fwd/Rev rod, the head baseplate is also used to control meshing of the takeup gear rotating the takeup reel table for play.

While the Fwd/Rev rod controls meshing of the takeup gear during play, movement of the head baseplate is utilized to control the takeup gear not to get in mesh with the gear of the reel table during STOP, FF (REW), and TPS FF (TPS REW).

As shown in Fig. 9, when the head baseplate is in position other than play, the part A of the head baseplate pushes part B of the takeup arm to keep the takeup gear from getting in mesh with the gear of the reel table.

Fig. 9 Takeup gear meshing control

## 4. Loading/Ejection Mechanism

## 4-1. Loading and ejection

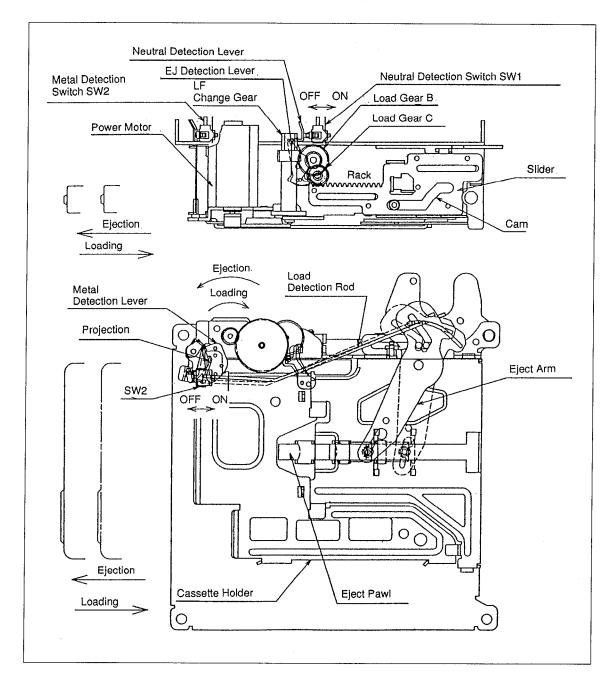

## 4-1-1. Loading

- (1) When the main gear is at the stop mode station, the gears from the power motor drives LF change gear mesh with the load gear B. This condition allows the cassette loading and ejection by the power motor. (see Fig. 10)

- (2) CW rotation of the power motor moves the slider and the ejection pawl to pull in the cassette horizontally.

- (3) Further CW rotation causes the cassette holder to descend by the cam mounted on the slider.

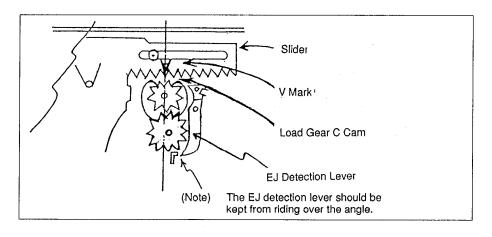

- Neutral detection switch SW1 is used to detect the beginning and the end of action. This switch, actuated by the cam provided on the flank of the load gear C and by the EJ detection lever, turns OFF at both ends of loading and ejection..

- \* Since SW1 turns OFF at the end of loading, it can be used freely at the main gear's stations except the STOP mode station and is also used for the sub-gear's neutral detection.

## 4-1-2. Ejection

Ejection is carried out by CCW rotation of the power motor. Power Motor stop timing is detected by the neutral detection switch SW1 turning OFF.

## 4-2. Metal detection switch functions

The metal detection switch has the following functions:

- 1. Tape loading start detection

- 2. Normal/Metal tape discrimination

## 4-2-1. Tape loading start detection

- (1) The metal detection switch SW2 is turned ON by the loading detection rod (linked with the eject arm) and the metal detection lever after the tape is ejected.

- (2) By slightly inserting the cassette, the eject arm turns and, through the middle of the loading detection rod and metal detection lever, sets SW2 to the OFF position.

- (3) When SW2 is turned OFF, the microcomputer detects insertion of the cassette and then the loading action starts.

## 4-2-2. Normal/Metal tape discrimination

Upon the loading of the cassette, the metal detection switch SW2, which can be turned ON and OFF automatically by the cassette tape.

Since the metal detection lever has a projection to enter the metal detection hole of the cassette, it sets SW2 to ON if the tape is a normal one, and sets SW2 to OFF if the tape is a chrome-dioxide or metal one.

Fig. 10 Loading/ejection mechanism

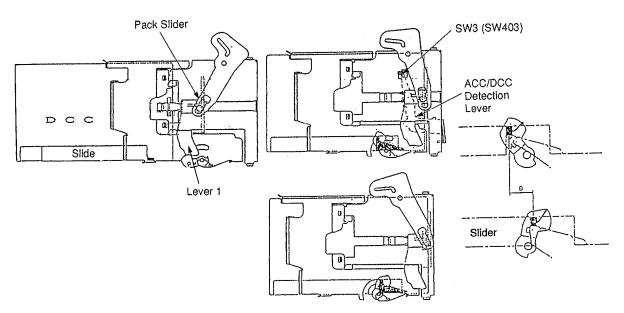

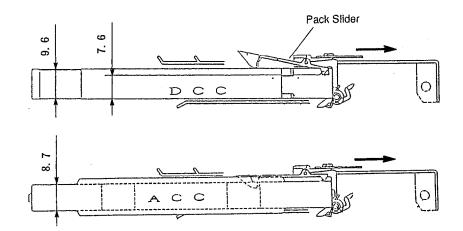

## **5. DCC TAPE DETECTION**

When the DCC tape is inserted, the pack slider is moved to inward. And the lever (1) is moved for arrow direction shown then the slider of DCC moves for opening tape part.

When the DCC tape is set into the cassette holder, the DCC detection lever moves outward to turn on the DCC/ ACC detection switch SW3 (SW903).

## 6. Mechanism Mounting & Adjustment Points

## 6-1. Load gear C mounting instructions

\* Align the V mark on the lift slider gear part with the center of the cam part of the load gear C cam.

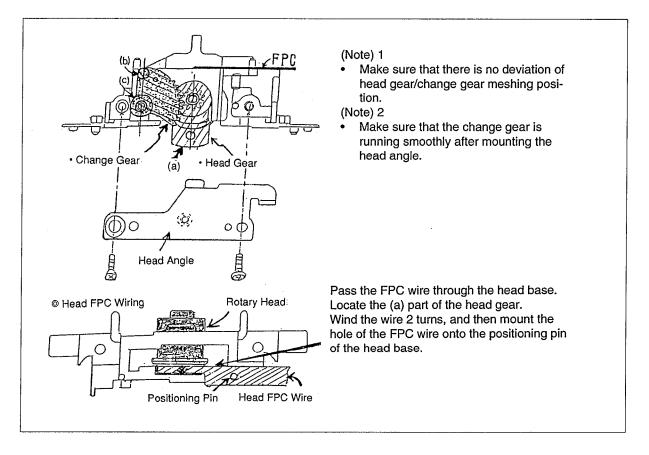

## 6-2. Head gear and change gear mounting instructions

- (1) Locate the (a) part of the head gear .

- (2) Keeping the change gear's (b) and (c) parts in a vertical straight line, make the gear teeth mesh.

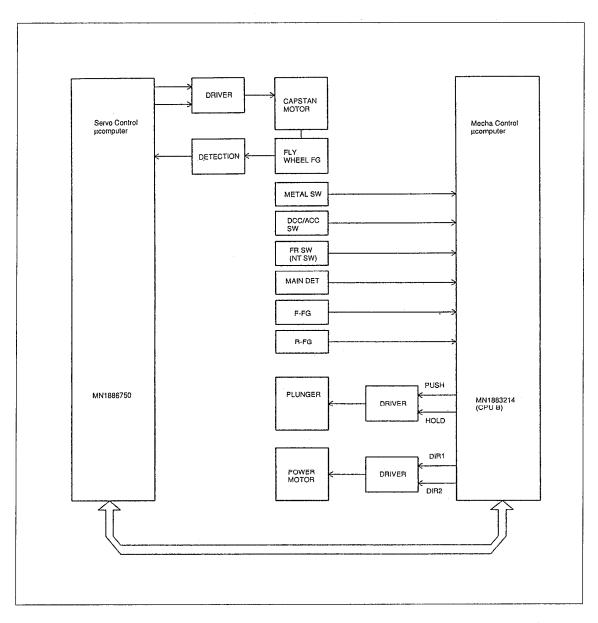

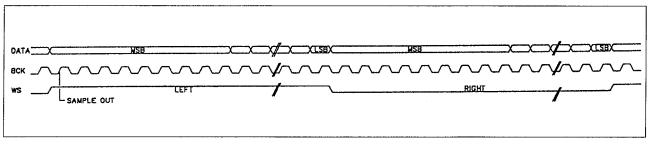

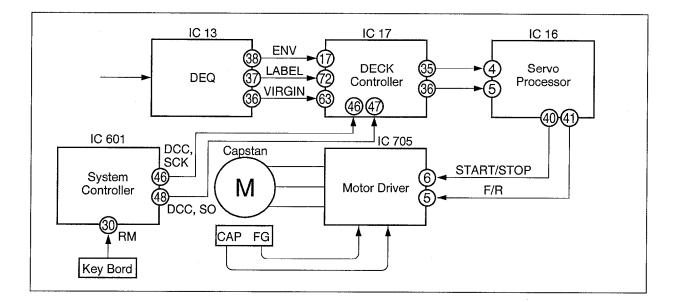

## 4. MECHANISM CONTROL BLOCK

(

ĺ

ĺ

(

Fig. 10 Mechanism control block

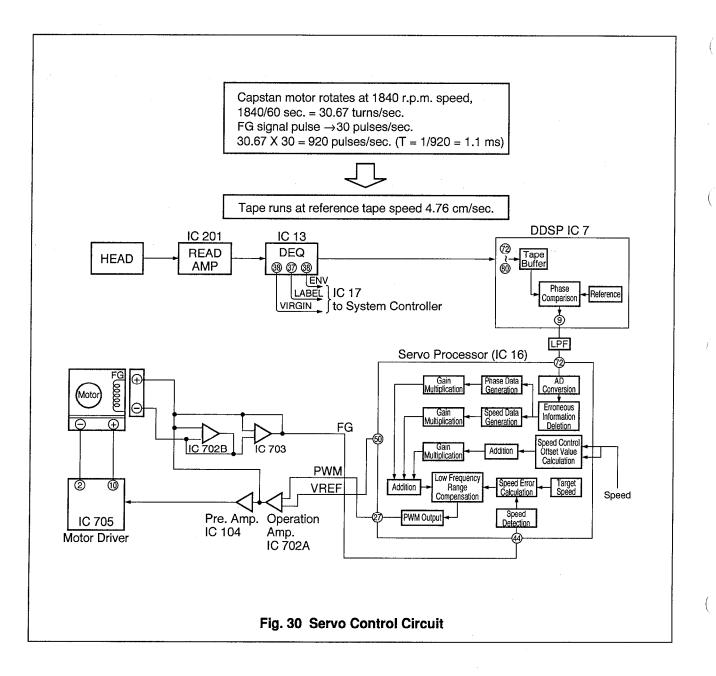

## **1. CAPSTAN MOTOR CONTROL**

Servo  $\mu$ -con is controled by pin 35 and 36 of main microcomputer and servo  $\mu$ -con controls capstan motor.

| MAIN μ-CON OUTPUT |           | MAIN μ-CON INPUT  |           |                 |

|-------------------|-----------|-------------------|-----------|-----------------|

| (Pin 36)          | (Pin 35)  | (Pin 55) (Pin 54) |           | MOTOR CONDITION |

| Pspd_set1         | Pspd_set2 | Pspd_mon1         | Pspd_mon2 |                 |

| L                 | L         | L                 | L         | NORMAL SPEED    |

| Н                 | L         | Н                 | L         | 0.5 TIMES SPEED |

| L                 | Н         | L                 | Н         | 2 TIMES SPEED   |

| Н                 | Н         | Н                 | Н         | STOP            |

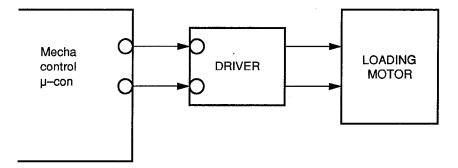

## 2. Loading Motor Control

Forward and reverse of the power motor is controled by pin 66 and pin 67 of the mechanism  $\mu$ -con.

## **Control Losic**

| μ-CON OUTPUT |         | DRIVER OUTPUT |             |                 |

|--------------|---------|---------------|-------------|-----------------|

| Pin 66       | Pin 67  | POWER M+      | POWER M-    | MOTOR CONDITION |

| (Pdir1)      | (Pdir2) |               |             |                 |

| L            | L       | "OFF" state   | "OFF" state | STOP            |

| Н            | L       | H             | L           | FORWARD         |

| L            | Н       | L             | н           | REVERSE         |

| Н            | Н       | L             | L           | BRAKE           |

## Plunger (solenoid) Control

Solenoid is controlled by pin 64 and pin 62 of Mecha- $\mu$ -con.

Pin 64 ("H") ..... Solenoid Active Mode

Pin 62 ("H") ..... Solenoid Hold Mode

Plunger control is as shown below.

| $\rightarrow$ | Pin 64        | :                    | Н                                                                                                                                                                                            |

|---------------|---------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\rightarrow$ | Pin 64        | :                    | L                                                                                                                                                                                            |

|               | Pin 62        | :                    | Н                                                                                                                                                                                            |

| $\rightarrow$ | Pin 62        |                      | L                                                                                                                                                                                            |

|               | $\rightarrow$ | $\rightarrow$ Pin 64 | $\begin{array}{rrrr} \rightarrow & \operatorname{Pin} 64 & : \\ \rightarrow & \operatorname{Pin} 64 & : \\ & & \operatorname{Pin} 62 & : \\ \rightarrow & \operatorname{Pin} 62 \end{array}$ |

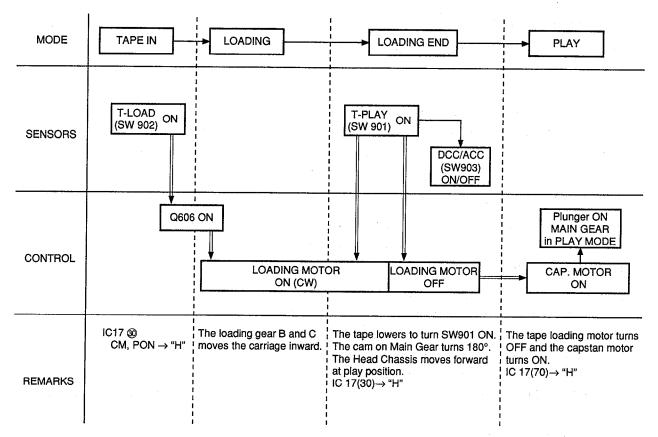

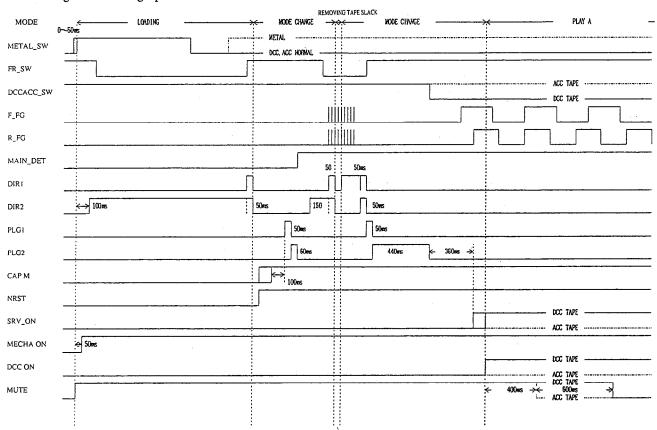

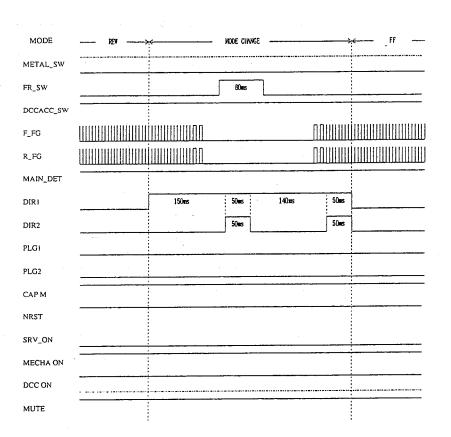

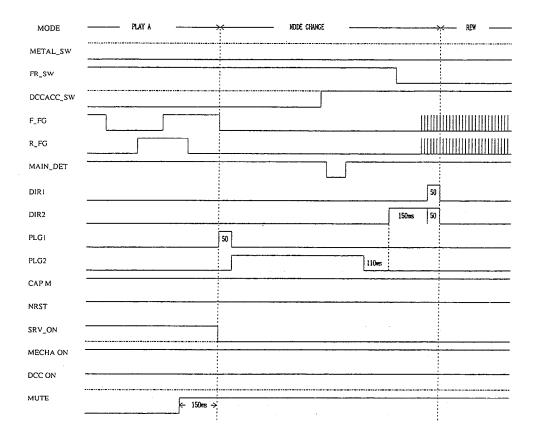

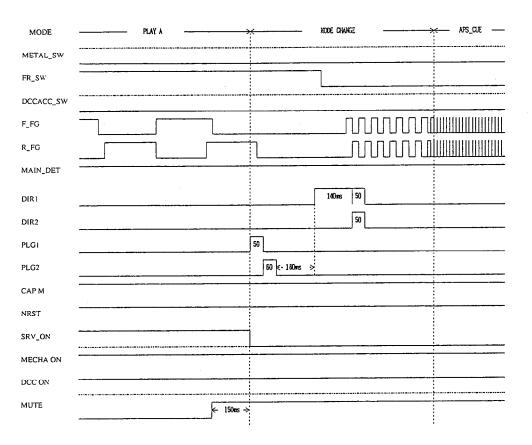

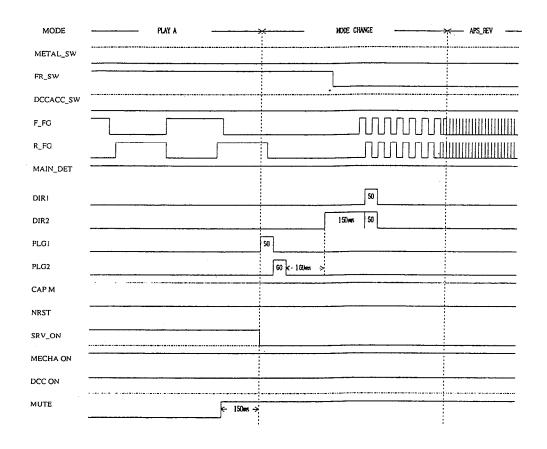

## 5 DECK TIMING CHART

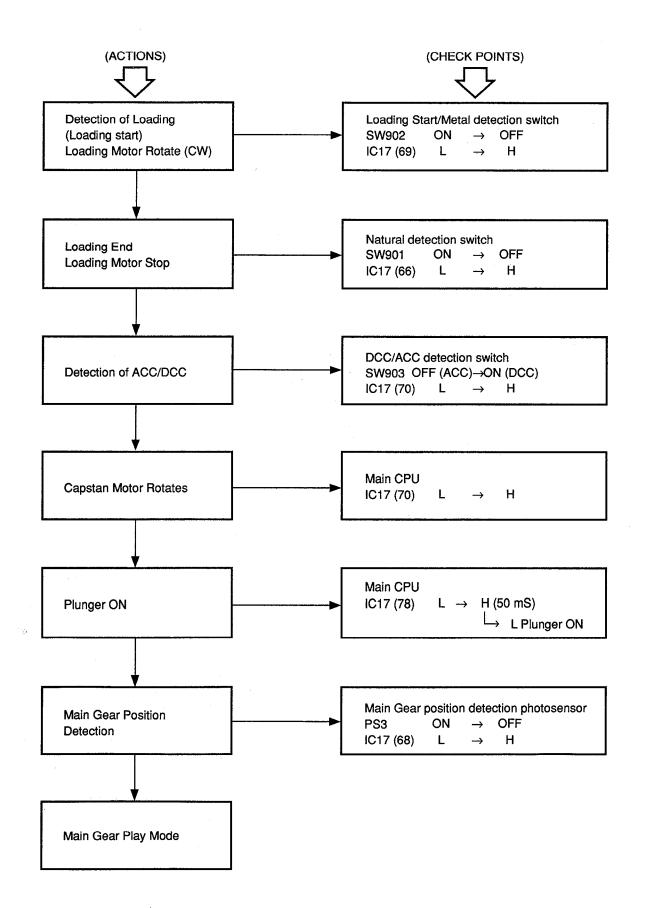

#### 1. Loading $\rightarrow$ Removing tape slack $\rightarrow$ PLAY A

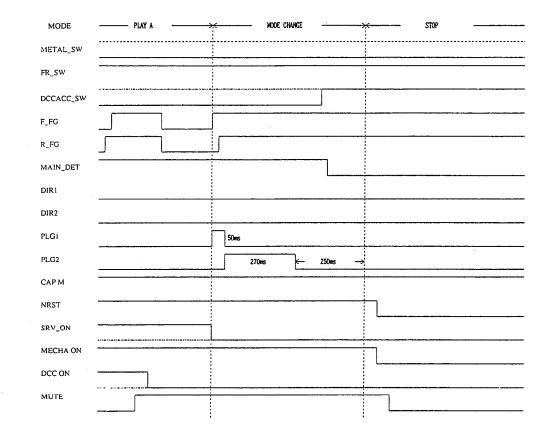

## 2. PLAY A $\rightarrow$ EJECT

| 50ms         |

|--------------|

| <b>200</b> 5 |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

| · ·····      |

| 50ws         |

|              |

|              |

|              |

|              |

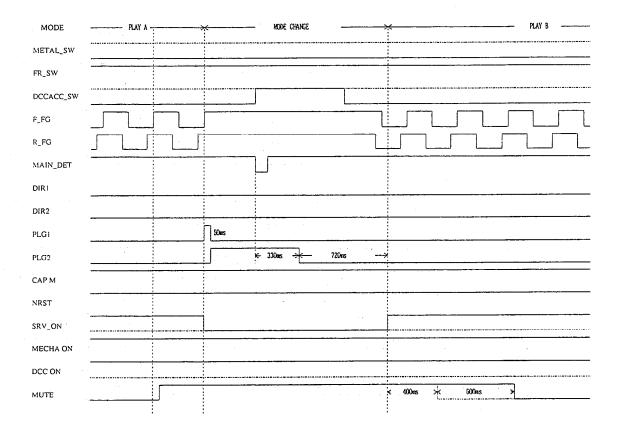

## 4. PROGRAM CHANGE $(B \rightarrow A)$

- 48 -

Ĵ.

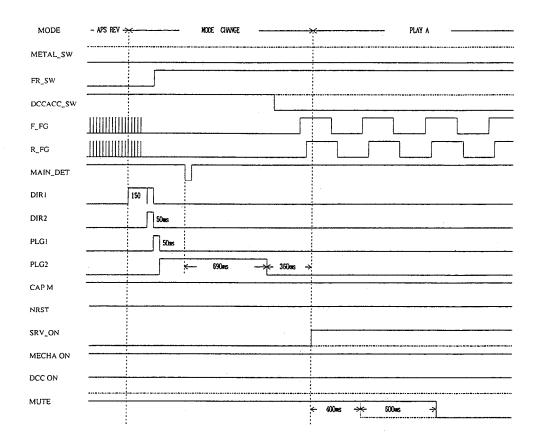

## 6. REW $\rightarrow$ PLAY A

- 49 -

Ĺ

8. REW  $\rightarrow$  FF

#### 10. APS\_REV $\rightarrow$ PLAY\_A

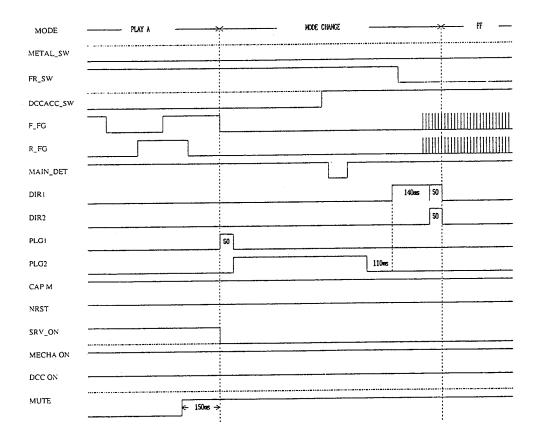

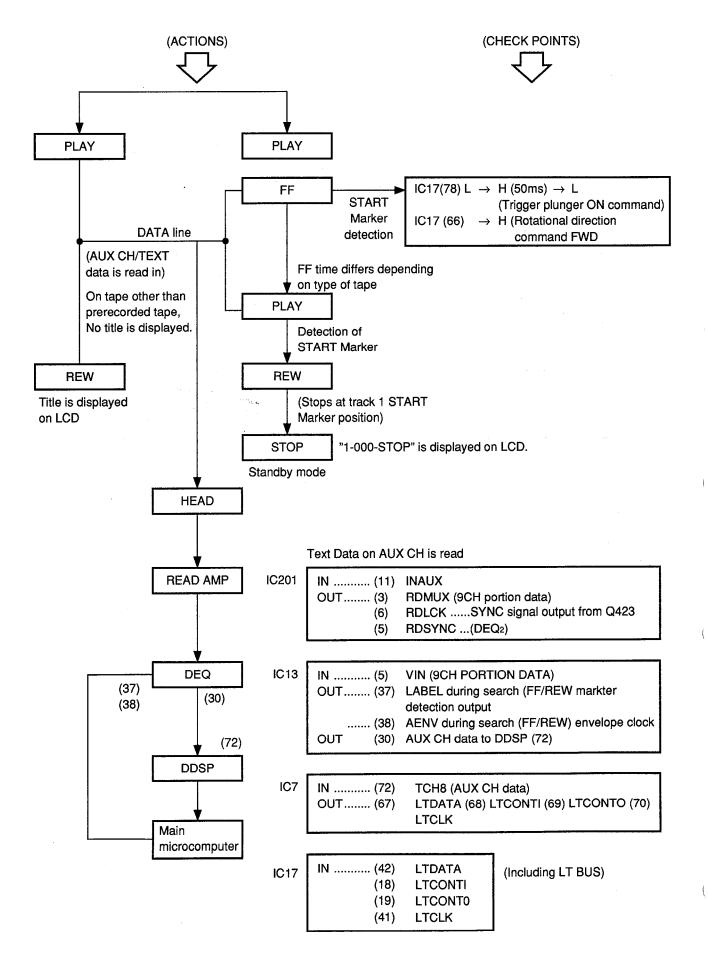

12. PLAY A  $\rightarrow$  FF

#### 14. PLAY A $\rightarrow$ APS CUE

## 15. PLAY A $\rightarrow$ APS REV

í

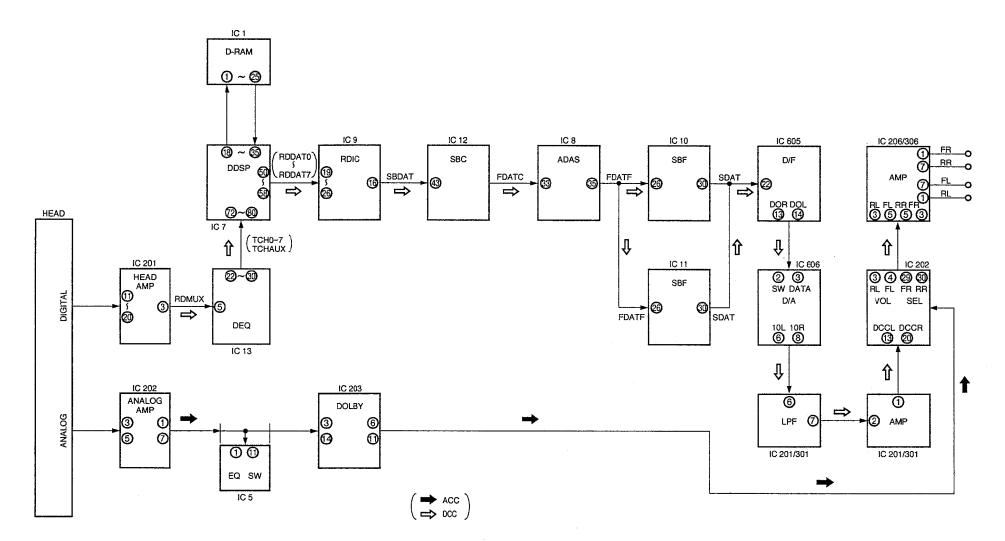

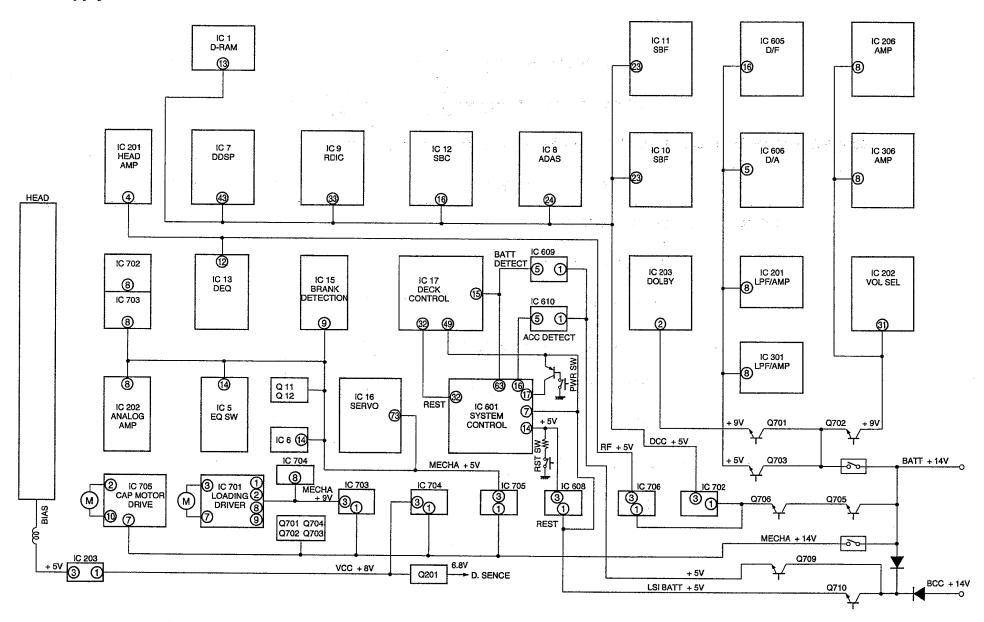

## EXPLANATION OF DCC CIRCUIT

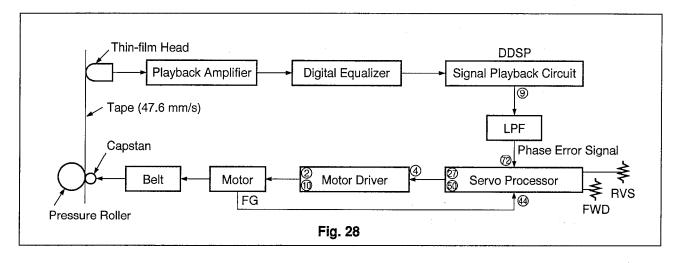

## 1. Flow of Signals and Function of Each Block

## **DDC Data Signal Line**

- Data taken out from the head is input to IC201 Pins (1), ~ (2) IC201 is a read amplifier sending data through BPF (which allows effective bands only) built in this IC. Then the data is output from Pin (3) (RDMUX).

- Data input to DEQ\_IC13 Pin (5) (PBDAT) undergoes waveform equalization (waveform shaping) in IC13, and respective CH data are individually output from Pins (2) ~ (30)

- CH data input respectively to (DDSP) IC7 Pin <sup>®</sup> ~ <sup>®</sup> are demodulated (10 → 8), and when each CH data is stored in DRAM (IC1) temporarily and read out, the cross interrib is released and the data is output through IC9 Pin <sup>®</sup> (SBDAT).

- DATA input to SBC IC12 Pin (3) is reformed into the PASC data format in IC12, and after the bit-compressed data is extended to the original state, it is output from Pin (3) (FDATC).

- Data input to (ADAS) IC8 Pin (3) to calculates the masking power of the sub-band signals and adds the masking threshold, and the data is output from Pin (2) (FDATF).

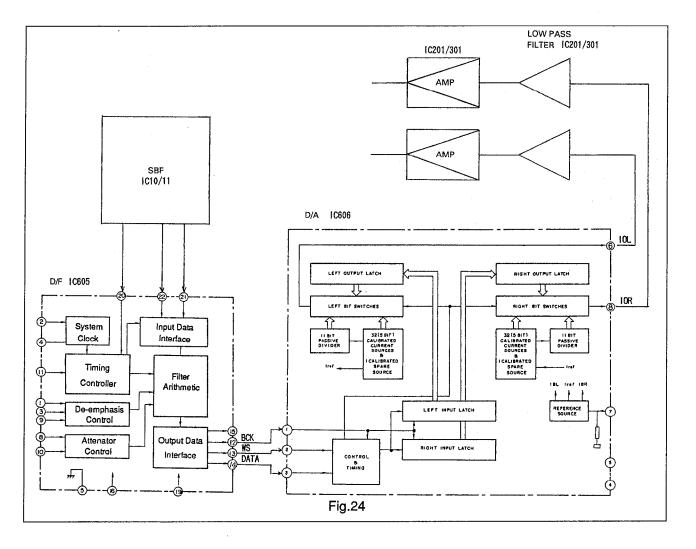

- Data input to SBF IC10 & IC11 to split a single broad-hand digital audio signal into 32 sub-bands or combining 32 sub-band into a single broud-band digital audio signal and the data output from Pin (30 (SDAT).

- Data input to the digital filter (DF) IC605 Pin @ undergoes digital filtration and LCH/RCH separation in IC605, the LCH data is output from Pin (a), and the RCH data from Pin (a). These are input to D/A converter (IC606) Pins (2) and (3), returned into analog signals, output from Pin (6) (LCH) and Pin (8) (RCH), and after passing through LPF, they are supplied to L/RCH LINE OUT terminals.

## ACC Signal Line

• The analog signals taken out from the head, is input to playback amp IC202 Pins ③ and ⑤. The LCH and RCH signals are output from Pins ① and ⑦ respectively, and passing through the Dolby IC (IC203), they are supplied to LCH/RCH LINE OUT terminals.

## Outline of Signal Line (DCC/ACC)

~

~~~

- 56 -

- 57 -

.

# 3. Descrption of Signal Names

| SIGNAL<br>NAME | FUNCTION                       | SIGNAL FLOW                   | Freq.         | EXPLANATION                                                                                      |

|----------------|--------------------------------|-------------------------------|---------------|--------------------------------------------------------------------------------------------------|

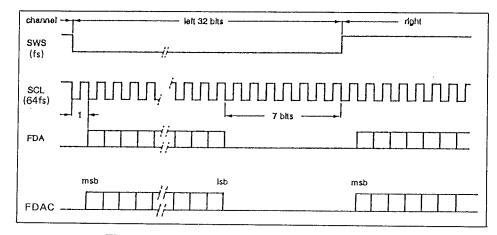

| FDA<br>FDAC    | FILTERED DATA<br>FILTERED DATA | SBF ──► ADAS<br>ADAS ─► SBC   |               | DATA TRANSFER IN I <sup>2</sup> S FORMAT, CARRING<br>32 SUB-BAND CHANNELS DIGITAL AUDIO<br>DATA. |

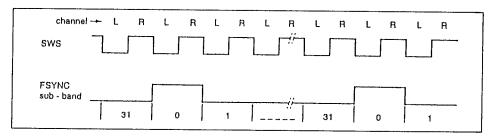

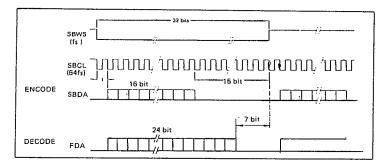

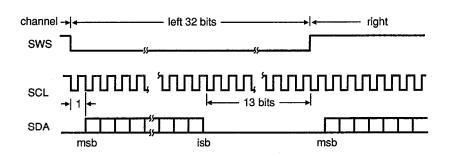

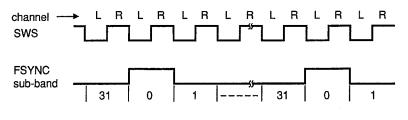

| sws            | WORD SELECT                    | SBC ADAS<br>SBF<br>ADC<br>D/F | fs            | SBC IS MASTER IN PLAY MODE.                                                                      |

| SCL            | SERIAL CLOCK                   | SBC                           | 64 fs         | BIT CLOCK FOR I'S INTERFACE                                                                      |

| FSYNC          | FILTER SYNC.                   | SBC                           | fs/32         | SBC PERMIT ONLY TRANSFER OF SUB-<br>BAND 0 DATA DURING FSYNC.                                    |

| S24<br>(CLK24) | MASTER CLOCK                   |                               | 24.576<br>MHz | F24 IS TO DETERMINE THE LENGTH OF<br>TYPE FRAME AND INTER FRAME GAP.                             |

| 256 fs         | SYSTEM CLOCK                   | SBC SBF<br>ADAS<br>ADC<br>DAC | 256 fs        | IN PLAY MODE, SBC IS THE MASTER AND SUPPLIES 256 fs.                                             |

| FDIR           | DIRECTION<br>CONTROL           | SBC SBF                       | H/L           | FDIR = 1 (DECODE MODE/PLAY)<br>FDIR = 0 (ENCORE MODE/REC)                                        |

| SBCL<br>(CLAB) | SUB-BAND CLOCK                 | SBC ERC0                      | 64 fs         | SBCL IS PART OF I <sup>2</sup> S INTERFACE AND<br>PROVIDES THE BIT CLOCK.                        |

| LT-BUS         | LTDATA                         | μC → ADAS                     |               | SERIAL DATA LINE                                                                                 |

|                | LTCONT0<br>LTCONT1             |                               |               | CONTROL LINE OF LT INTERFACE FROM<br>MICROCONTROLLER.                                            |

|                | LT CLOCK                       |                               |               | BIT CLOCK FOR THE LT INTERFACE.                                                                  |

| ED0 ~ ED9      | ERCO DATA LINE                 | DDSP ERCO                     |               | PARALLEL DATA FOR SYMBOL TRANSFER<br>(SAME AS DATA 0 ~ 7/FLAG 1 ~ 2)                             |

| SBEF           | SUB-BAND<br>ERROR FLAG         | ERCO SBC                      |               | ERROR FLAG TRANSFERRED TO SBC                                                                    |

| REST           | RESET                          |                               |               | HARDWARE RESET                                                                                   |

| LT SUBBUS      | LT INTERFACE                   | ADAS SBC                      |               | LT-INTERFACE FOR COMMUNICATION.<br>ADAS IS THE MASTER                                            |

| MCLK           | MASTER CLOCK                   | DDSP ERC0                     | 6.144<br>MHz  | THIS CLOCK (128 fs) IS USED FOR THE SYMBOLS TRANSFER.                                            |

| MPCL           | CLOCK PHASE<br>REFERENCE       | DDSP ERC0                     | 3.072<br>MHz  | THIS CLOCK (64 fs) IS USED FOR CLOCK<br>PHASE REFERENCE SIGNAL.                                  |

| RDMUX          | READ<br>MUCTIPLEX              | READA→ DEQ                    |               | READ MULTIPLEXER OUTPUT.                                                                         |

## **Descrption of Signal Names**

Ĺ

$\left( \right)$

| SIGNAL<br>NAME      | FUNCTION                 | SIGNAL FLOW         | Freq.        | EXPLANATION                                                                                       |

|---------------------|--------------------------|---------------------|--------------|---------------------------------------------------------------------------------------------------|

| RDCLK               | READ CLOCK               | DEQ READ            | 960<br>MHz   | DATA CLOCK FOR READ AMP. DATA OF 8<br>CH AND 1 AUX CH IS TRANSFERED DUR-<br>ING 10 RDCLK PERIODS  |

| RDSYNC              | READ SYNC.               |                     |              | CONTROL OUTPUT OF DEQ TO SYNCHRO-<br>NIZE THE READ AMP.                                           |

| СН0 ~ СН7           | DATA LINE                | DEQ DDSP            |              | REQ CHANNEL n OUTPUT                                                                              |

| SPEED               | SPEED CONTROL            | DDSP SERVO          |              | PWM CONTROL SIGNAL FOR CAPSTAN                                                                    |

| STRTSEG             | START SEGMENT            | DDSP► μc            |              | STRTSEG IS USED AS A TIMING FOR<br>TRANSFER OF SYSINFO AND AUX                                    |

| SBDIR               | SUB BAND<br>DIRECTION    | DDSP                |              | DIRECTION OF DATA FLOW BETWEEN<br>ERCO AND SBC ON SBDA LINE                                       |

| LABEL               | LABEL                    | DEQ <del>→</del> μc |              | SEARCH MODE LABEL DETECTION LABEL<br>FOUND IN THE AUX-CH                                          |

| AEMV                | ALTERNATING<br>ENVELOPE  | DEQ <del></del> μc  |              | MONITORS DURING SEARCH MODE THE<br>START OF A TRACK (FROM AUX-CH)                                 |

| VIRGIN              | VIRGIN<br>DETECTION      | DEQ──► μc           |              | INFORM THE $\mu c$ A BLANK TAPE IS INSERTED                                                       |

| RDATA<br>0 ~ 3 (RD) | RAM DATA BUS             | DDSP DRAM           |              | BATA BUS LINE.                                                                                    |

| ADRS0 ~ 7<br>(RA)   | ADDRESS LINES            | DDSP DRAM           |              | 8 ADDRESS LINES TO DRAM TO LOCATE<br>ADDRESS FOR WRITING DATA INTO OR<br>READING DATA FROM MEMORY |

| AUX                 | AUX-CH OUTPUT            | DEQ DDSP            |              | SLICED OUTPUT FROM DEQ OF AUX-CH<br>DATA                                                          |

| DOL/DOR             | DIGITAL OUTPUT           | D/F> D/A            |              | SERIAL DATA OUTPUT                                                                                |

| ВСК0                | BIT CLOCK                | D/F D/A             |              | CLOCK SIGNAL                                                                                      |

| WCK0                | WORD CLOCK               | D/F D/A             | 3.072<br>MHz | INDICATE WHETHER DATA FOR L-CH, OR<br>R-CH                                                        |

| SBMCLK              | SUB-BAND<br>MASTER CLOCK | SBC ERCO            | 6.144<br>MHz |                                                                                                   |

(

## **PASC/Precision Adaptive Sub-band Coding**

Precision Adaptive Sub-band Coding achieves highly efficient digital encoding of audio signals by using an algorithm based on the characteristics of the human auditory system.

The broad-band audio shignal is split into 32 sub-band signals during encoding. For each of the sub-band signals the masking threshold is calculated. The samples of the sub-bands are incorporated in the PASC signal with an accuracy that is determind by the singal to masking threshold ratio for that sub-band.

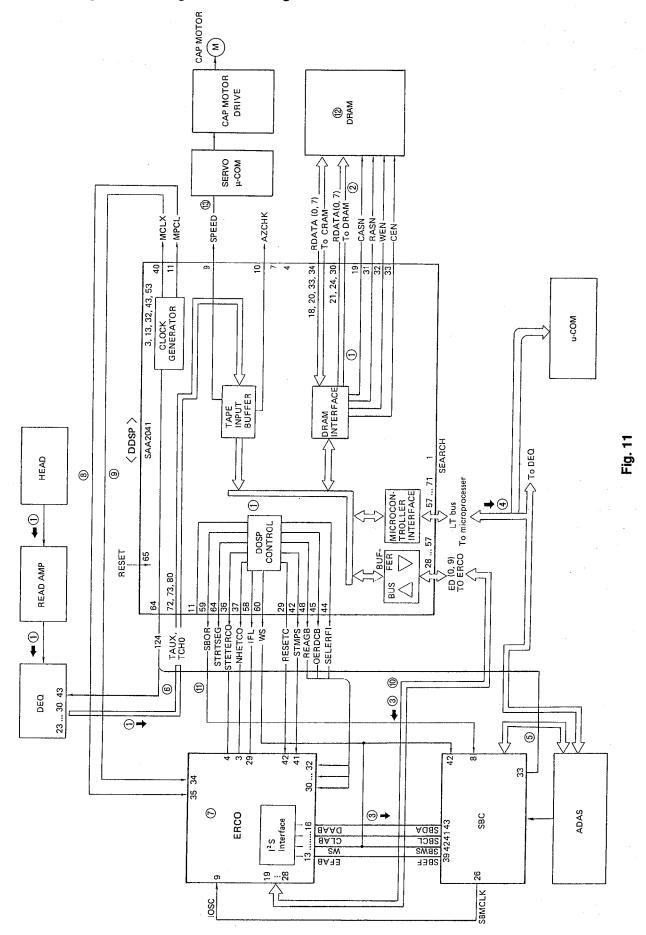

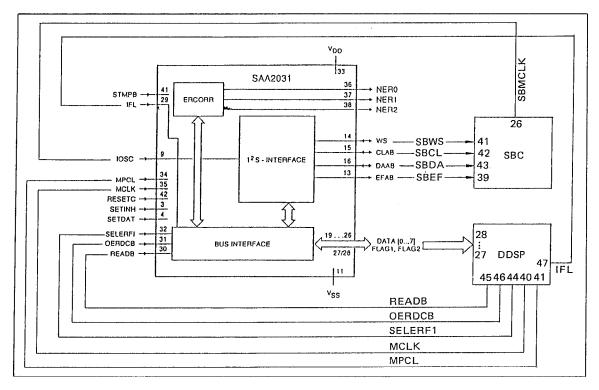

## **DDSP**/Digital Drive Signal Processing

Performing digital signal processing within the DCC (Digital Compact Cassette) system, the DDSP (Digital Drive Signal Processing; SAA2041) device possesses control, address generation and data formation functions within the system. Its main functions include control of the ERCO (SAA2031) device together with the processing of data from the DEQ (SAA2051).

## SBC/Sub-band Coder and Decoder

When encoding audio data, the SBF (sub-band filter, SAA2001) devices split the incoming signals at the sample frequency (f2) into 32 sub-bands. The SBC (Sub-band Coder and Decoder, SAA2021) performs the signal encoding. Different bit-rates can be used for data transfer.

During the decoding of data, the SBC (SAA2021) reconstructs the sub-band signals for application to the SBF (SAA2001) devices which reconstitute the sub-band signals into a single digital audio signal.

The input and output system data are digital samples of an audio signal represented in 24-bit two's complement. The sub-band samples are represented in 24-bit two's complement notation.

## **ERCORR/Error Correction**

The Error Correction/Decoder is designed for Reed Solomon codes over GF (256) of distance 5 or 7 at a maximum code word length of 32 symbols:

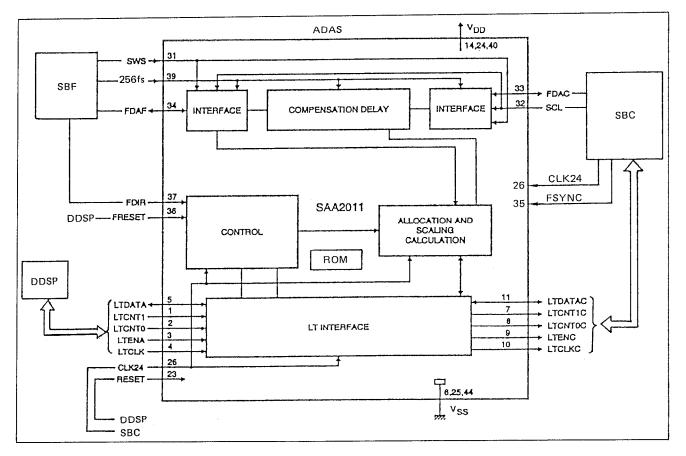

## **ADAS/Adaptive Allocation and Scaling**

The PASC system calculates the masking power of the sub-band signals and adds the masking threshold. Sub-band signals with power below this threshold denote information to be discarded. Non-masked signals are coded using floating point notation in which a mantissa corresponds in length to the difference between peak power and masking threshold. The process is repeated for every PASC frame and is known as the Adaptive Allocation of the available capacity.

## **SBF/Sub Band Filter**

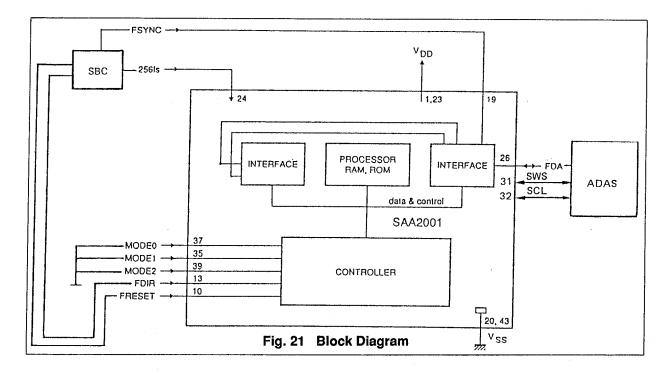

Per forming the splitting or combining function in the Precision Adaptive Sub-band Coding (PASC) system, the SAA2001 is a Sub-Band Filter (SBF) intended for use in conjunction with the ADAS (Adaptive Allocation and Scaling; SAA2011) and SBC (Sub-band Coder/ Decoder; SAA2021) devices. It is capable of splitting a single aroar-band digital.

In a complete stereo (or 2-channel mono) PASC system, two SAA2001 devices are required; one for each channel.

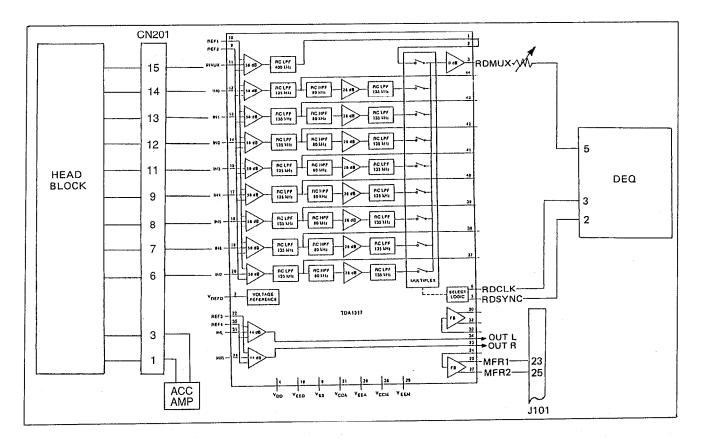

## 5. DCC Read Amplifier

## Feedback Amplifiers

Two feedback amplifiers are provided for driving a coil in the Compact Cassette MRH. This provides a feedback loop in order to improve the linearity of the analog audio response.

## Multiplexer

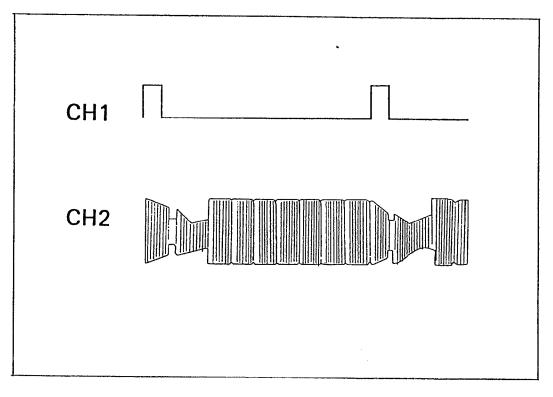

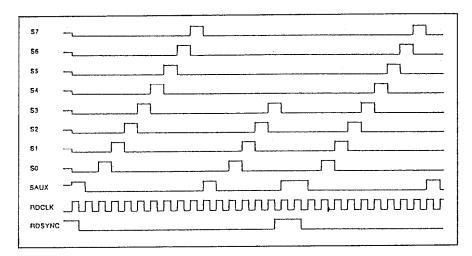

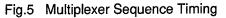

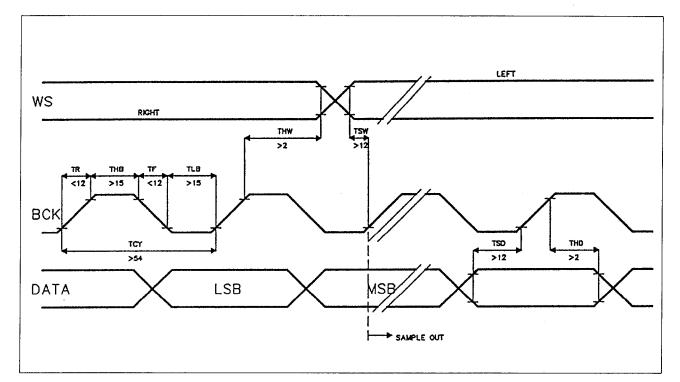

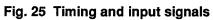

The IC employs a multiplexer circuit to switch the digital channels, sequentially, to the output. The effective sampling frequency is one tenth of the clock frequency at RD CLK (pin 6). A timing diagram is given in Fig. 5

Fig. 4

## 6. DEQ/Digital Equilizer

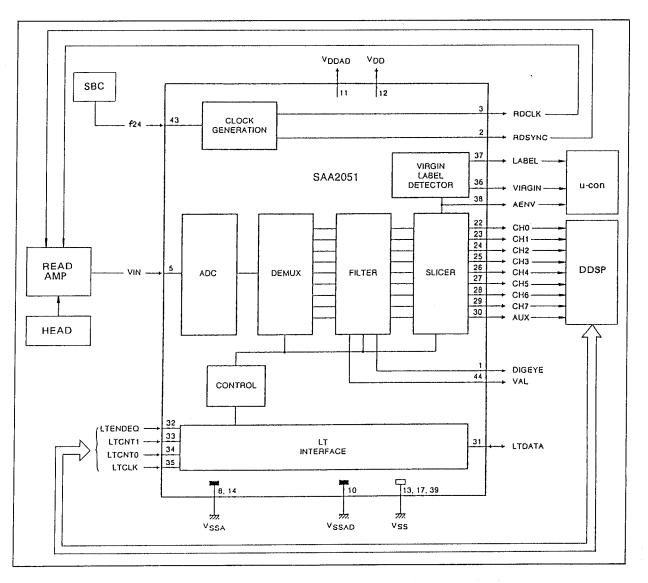

## FUNCTIONAL DESCRPTION

## Operational Modes

DEQ operating modes are programmed via the LT interface:

#### NORMAL

- AD conversion

- demultiplexing

- equalization

- · zero crossing

In this mode the DEQ (SAA2051) performs the equalization and slicing of the eight data channels and the auxiliary channel. The eight data channels have a bit-rate of 96 Kbit/s while the auxiliary channels has a bit-rate of 12 Kbit/s.

The DEQ (SAA2051) input is a time-multiplexed analogue signal from the Read Amplifier. The signal contains ten time slots, of which nine are used. The Read Amplifier and the DEQ (SAA2051) synchronize with the RDCLK and RDSYNC signals generated by the DEQ (SAA2051).

Following A/D conversion and demultiplexing the nine channels are equalized. The encoding of the equalizing coefficients (12 per channel) are not fixed and must be loaded via the LT interface before operation.

The nine equalized output signals are up-sampled by a factor of 10 with the resulting signals fed to the slicer. The slicer output is applied to the DDSP (SAA2041).

Fig. 6

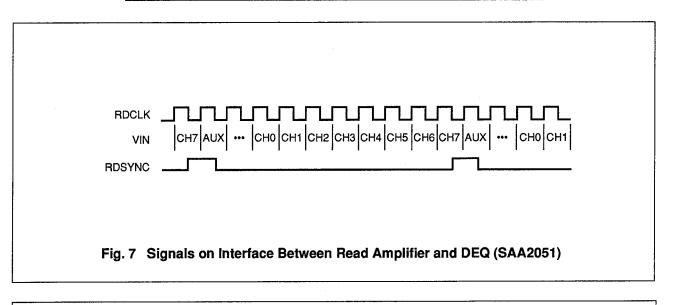

The interface between the Read Amplifier and the DEQ (SA2051) consists of three signals:

VIN from Read Amplifier to DEQ (SAA2051); time multiplexed data

RDSYNC from DEQ (SAA2051) to Read Amplifier; synchronization between Read Amplifier multiplexer and DEQ demultiplexer RDCLK from DEQ (SAA2051) to Read Amplifier; data clock for Read Amplifier multiplexer

The multiplexed VIN output of the Read Amplifier; changes to another channel at the rising edge of RDCLK. RDSYNC synchronizes the Read Amplifier VIN output: If RDSYNC is HIGH, the rising edge of the RDCLK will select the AUX channel.

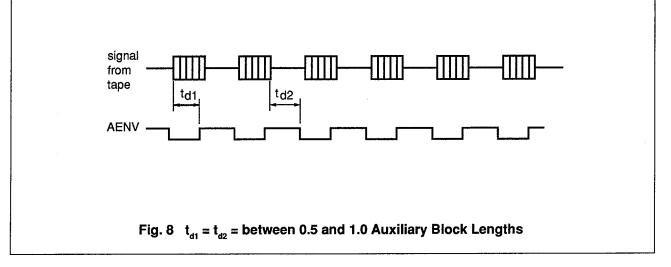

Figs. 7 and 8 show the relation ship between DEQ (SAA2051) and the Read Amplifier.

## Table 1 Dependency of Read Amplifier on Operational Mode

| OPERATIONAL MODE | RDSYNC | RDCLK |

|------------------|--------|-------|

| normal           | YES    | YES   |

| test             | YES    | YES   |

| search           | HIGH   | YES   |

| OFF              | HIGH   | HIGH  |

## LABEL AND VIRGIN DETECTION INTERFACE

When the DCC player is in its search mode, the tape is fast-wound while the head retains tape contact. The DEQ (SAA2051) can be made to operate in the search mode and the information will be read from the auxiliary tape track.

The following three signals are generated:

- LABEL label detection (HIGH if label is detected)

- VIRGIN virgin tape detection (HIGH if virgin tape is detected)

- AENV Alternating envelope (sliced envelope)

AENV, LABEL and VIRGIN are disabled in normal off modes. LABEL, VIRGIN and AENV are LOW. AENV, LABEL and VIRGIN are enabled when the DEQ (SAA2051) is in search mode.

The device detects the envelope AENV of the auxiliary track at search speeds between 3 and 50 times normal speed. If AENV is continuously HIGH (label detection), LABEL will be HIGH.

When AENV is continuously LOW (virgin tape detection) VIRGIN will be HIGH.

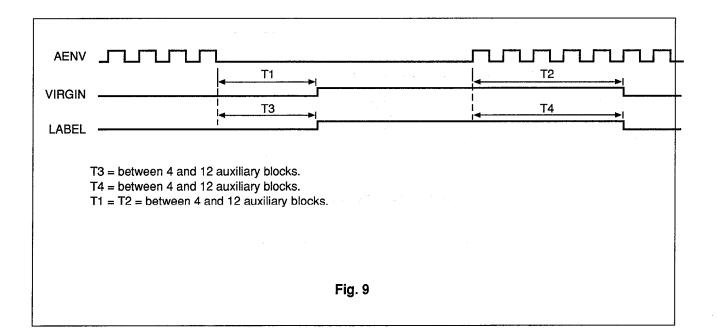

Figs. 9 show the relationship between AENV, VIRGIN and LABEL.

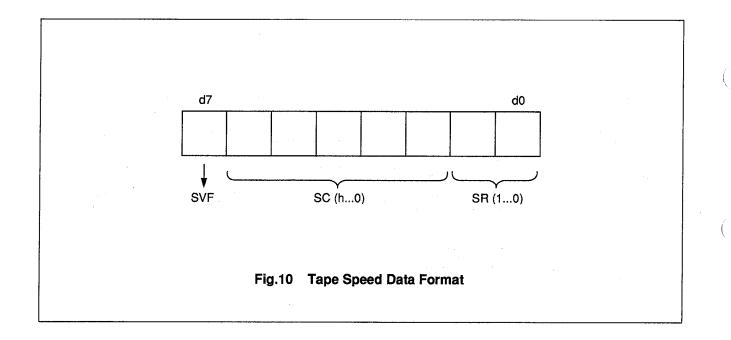

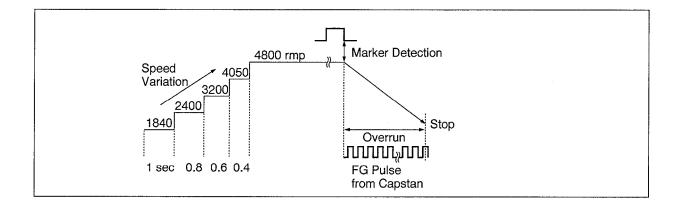

## LABELED TAPES SPEED CALCULATION

When the DCC player is in its search mode, the tape speed increases. LABEL informationis encoded throughout its length. To examine the length of a label, the tape speed must be known. In search mode the DEQ (SAA2051) assesses the speed of labelled tapes. The microcontroller obtains this information via the LTinterface.

The speed information is encoded in the three vari-

ables:

SVF Speed Validation Flag (HIGH if invalid)

SC (4 ... 0) Speed Counter

SR (1 ... 0) Speed Range

Search speed 2 \_\_\_\_\_

# 7. DDSP/Digital Drive Signal Processing

í

Ĺ

- 67 -

#### **DDSP**/Digital Drive Signal Processing

Performing digital signal processing within the DCC (Digital Compact Cassette) system, the DDSP (Digital Drive Signal Processing; SAA2041) device pocesses control, address generation and data formation functions within the system. Its main functions include control of the ERCO (SAA2031) device together with the processing of data from the DEQ (SAA 2051).

## **Functional Description**

## Modes

The DDSP (SAA2041) can be operated in any one of three modes:

DPAP (Data Play-back and Aux Play-back)

The DDSP synchronizes to the WS (I<sup>2</sup>S-interface word select) signal.

## DPAP Mode (DECODE)

In the data play-back/aux play-back mode, the equalized data from the mine tape tracks are fed to the DDSP (SAA2041) which recovers and demodulates the channel bit streams and stores them in the DRAM.

The DDSP (SAA2041) controls the flow of data to and from the ERCORR section of the  $\leftarrow$  (3) ERCO (SAA2031) device. When all the data has been processed the DDSP (SA2041) sends the sub-band data via the I<sup>2</sup>S-interface in the ERCO (SAA2031) to the SBC (SAA2021).

The AUX and SYSINFO data can be trans-  $\leftarrow @$  ferred to the microcontroller via the LT interface.

#### **Clock Interfacing**

The 24.576 MHz clock input is fed directly from the SBC (SAA2021) pin 124.

Interfacing the DDSP (SAA2041) to the Digital Equalizer. ← ⑤

Nine lines (TCH0...TCH7 and TAUX) connect the DDSP to the DEQ (SAA2051).  $\leftarrow$  6

#### **DPAR Mode**

When the system is set to the data play-back mode, the microprocessor must read SYSINFO from this device.

Equalized channel data from the 8 data carrying tracks are fed to the DDSP for recovery and demodu-

lation. The DDSP (SAA2041) stores this data in the DRAM.

# Interfacing the DDSP (SAA2041) to the ERCO (SAA2031)

The ERCO (SAA2031) provides the Reed  $\leftarrow \bigcirc$ Solomon error correction encoding and deconding for the DCC system and l<sup>2</sup>S-bus interfacing to the SBC (SAA2021).

The MCLK line provides the 6.144 MHz clock  $\leftarrow$  (8) signal connecting to the MCLK input of the ERCO (SAA2031) device.

The MPCL line provides the 3.072 MHz clock  $\leftarrow$  (9) phase reference signal which connects to the MPCL input of the ERCO (SAA2031) device. (This signal is not necessarily in phase with the WCLOCK line).

Data is transferred between the DDSP  $\leftarrow \bigcirc$ (SAA2041) and the ERCO (SAA2031) via a 10bit parallel bus (ED0-ED9).

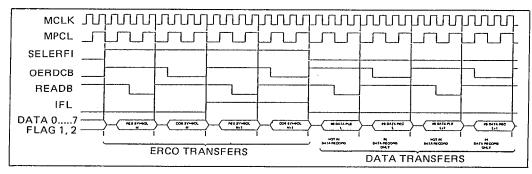

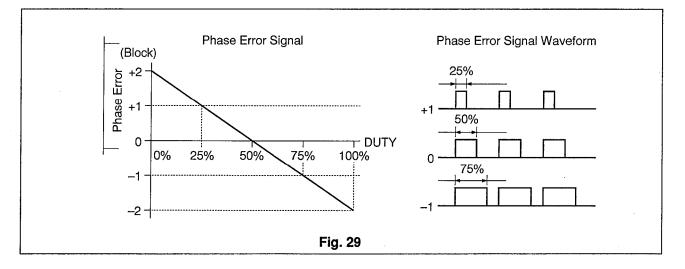

#### Interfacing to the SBC (SAA2021)